## LETTER • OPEN ACCESS

## Organic heterojunction transistors for mechanically flexible multivalued logic circuits

To cite this article: Debdatta Panigrahi et al 2021 Appl. Phys. Express 14 081004

View the article online for updates and enhancements.

https://doi.org/10.35848/1882-0786/ac122f

## Check for updates

LETTER

## Organic heterojunction transistors for mechanically flexible multivalued logic circuits

Debdatta Panigrahi<sup>1</sup>, Ryoma Hayakawa<sup>1</sup>, Kosuke Honma<sup>1,2</sup>, Kaname Kanai<sup>2</sup>, and Yutaka Wakayama<sup>1,2\*</sup>

<sup>1</sup>International Center for Materials Nanoarchitectonics (WPI-MANA), National Institute for Materials Science (NIMS), 1-1 Namiki, Tsukuba 305-0044, Japan

<sup>2</sup>Department of Physics, Faculty of Science and Technology, Tokyo University of Science, 2641 Yamazaki, Noda, Chiba 278-8510, Japan

\*E-mail: WAKAYAMA.Yutaka@nims.go.jp

Received June 9, 2021; revised June 22, 2021; accepted July 6, 2021; published online July 16, 2021

Organic multivalued logic circuits (OMVLs) have drawn tremendous attention due to their high data processability and simple fabrication techniques. However, OMVLs have so far been achieved only on rigid silicon substrates, and this limits their potential for broader applications. In this study, we develop an organic ternary inverter on plastic substrates. The inverters showed well-balanced ternary logic states with high voltage gain and low power consumption. Importantly, the devices exhibited stable operation even after 100 bending cycles, demonstrating high flexibility and reliability. This device has high potential to attain mechanical flexibility and data handling capability at the same time. © 2021 The Japan Society of Applied Physics

Supplementary material for this article is available online

Iexible, stretchable and lightweight electronic devices such as thin-film transistors, logic gates and integrated circuits (ICs) have received enormous attention due to their potential applications in the internet-of-things (IoT) and wearable electronics.<sup>1-5)</sup> Apart from their application to bendable flat panel displays, wearable and ultrathin ICs can also be used in the form of stickers as identification tags and in healthcare applications to monitor essential body parameters.<sup>6,7)</sup> Organic semiconductors play a pioneering role in advanced electronic applications such as this, not only due to their superior electrical and optical properties but also because of their intrinsic mechanical flexibility that enables the development of circuitry on practically any kind of common surface such as paper, plastics and fabrics.<sup>8-12)</sup> However, the chief limitation of organic electronics, i.e. low data processability, should be noted. This is because modern lithographic technologies cannot be applied to organic semiconductors. Multivalued logic circuits (MVLs) predominate in this regard, because they can exhibit three or more logical states, and thus can handle higher volumes of information than conventional binary logic circuits.13-20) Additionally, MVLs can drastically minimize chip area by reducing the number of constituent devices and enable the development of densely ICs.<sup>21-23)</sup> OMVLs are a potential game changer for next-generation IoT electronics, as they can achieve both high integration density and mechanical flexibility together with the advantage of easy patterning processes and low production costs. Several attempts have recently been made to develop high-performance OMVLs.<sup>24–26)</sup> In these studies, pn-heterojunctions played an important role in realizing ternary logic states. However, all were implemented on flat and rigid silicon substrates, which limits their range of potential applications. Flexible MVLs, therefore, need to be developed to be able to fully exploit the advantages of organic semiconductors and to further expand the low-power, wearable electronic application prospects of these ICs.

In this study, we tackled this key challenge by developing a flexible organic ternary logic circuit. The logic circuit is constructed by combining an n-type transistor and a heterojunction transistor (HT) that consists of two organic semiconductors:

PhC<sub>2</sub>H<sub>4</sub>-benzo[de]isoquinolino[1,8-gh]quinolone diimide (PhC2-BQQDI) and 2,7-dioctyl[1]benzothieno[3,2-b][1]benzothiophene (C8-BTBT) as n-type and p-type semiconductors, respectively.<sup>27,28</sup>) Other key materials are insulating films that act as gate dielectric layers. One is poly (methyl methacrylate) (PMMA), which is used to prioritize mechanical flexibility. The other is hafnium oxide (HfO<sub>2</sub>), which is employed specifically for low-voltage operation owing to its high dielectric constant. The inverters with both dielectric layers exhibit well-balanced ternary logic states, full-swing operation and high gain values. Most importantly, the inverters operated steadily after several cycles of repeated substrate bending, showing considerable potential for use in wearable electronic applications.

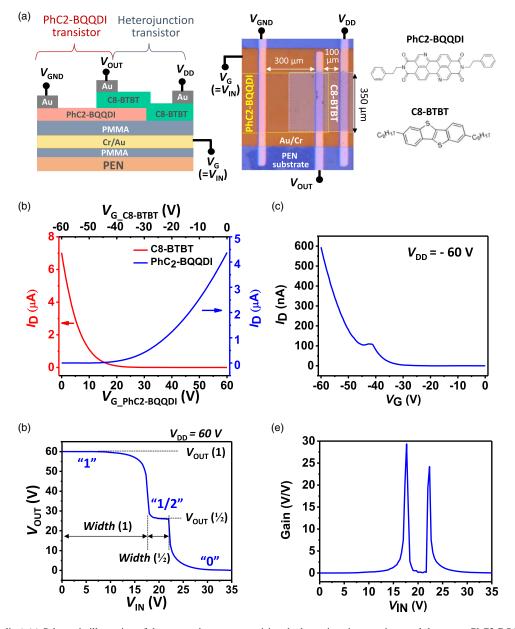

Figure 1(a) shows a schematic illustration of the ternary inverter with the PMMA dielectric layer, a top view photograph and the molecular structures of PhC2-BQQDI and C8-BTBT. The pn-heterojunction (C8-BTBT/PhC2-BQQDI) is formed between the  $V_{DD}-V_{OUT}$  electrodes. This part is therefore termed an HT. Meanwhile, the difference in  $V_{\text{GND}}$  and  $V_{\text{OUT}}$  provides the drain bias voltage for operating the n-type (PhC2-BQQDI) transistor. The device dimensions (width and lengths of the channels) are indicated in the photograph. The ternary inverter was implemented by combining the HT in series connection with a PhC2-BQQDI transistor on the flexible polyethylene naphthalate (PEN: DuPont Teijin, Teonex®) substrates. First, a 200 nm thick PMMA layer was spin-coated on the PEN substrates to reduce the surface roughness. Next, Cr (4 nm)/ Au (30 nm) bilayer electrodes were thermally evaporated to form the gate electrodes. On top of the gate electrodes, another PMMA (300 nm) layer was spin-coated to serve as the gate dielectric layer. Then, organic semiconducting layers, PhC2-BQQDI (≈16 nm) and C8-BTBT (≈19 nm), were thermally evaporated at a background pressure of  $10^{-7}$ Pa onto the PMMA surface as n-type and p-type channels,

Content from this work may be used under the terms of the Creative Commons Attribution 4.0 license. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

**Fig. 1.** (Color online) (a) Schematic illustration of the ternary inverter comprising the heterojunction transistor and the n-type PhC2-BQQDI transistor, top view photograph showing the device dimensions and chemical structures of PhC2-BQQDI and C8-BTBT. (b) Transfer characteristics at  $V_D = |60|$  V of the C8-BTBT (red line) and PhC2-BQQDI (blue line) transistors. (c) Transfer characteristics of the heterojunction transistor at  $V_{DD} = -60$  V. (d) Voltage transfer characteristics of the ternary inverter at  $V_{DD} = 60$  V. Parameters that define the device performance ( $V_{OUT}$  levels and  $V_{IN}$  widths) are also shown. (e) Gain profile of the inverters as a function of  $V_{IN}$ .

respectively, using corresponding shadow masks. These two channel layers were partially overlapped to form the heterojunction, which plays the most crucial role in yielding negative differential transconductance (NDT). Next, gold films, comprising the source and drain electrodes, were thermally evaporated using another shadow mask to complete the HT configuration. Finally, an additional electrode, namely, an output electrode, was simultaneously formed between the source and drain electrodes to monitor the output voltage ( $V_{OUT}$ ). Here, it should be noted that the C8-BTBT layer in the HT was connected from the source to the drain electrodes to obtain a high on-current at high  $V_{\rm G}$ region, as described by Kim et al.<sup>25)</sup>

Figure 1(b) shows the transfer curves of the C8-BTBT and PhC2-BQQDI transistors. These were measured individually by a semiconductor parameter analyzer (Agilent, B1500A), separately from the HT, to examine the fundamental

properties of the respective channels. The output curves are also shown in Fig. S1 in the supporting information for reference (available online at stacks.iop.org/APEX/14/ 081004/mmedia). All measurements were carried out at room temperature in an ambient atmosphere, in dark conditions. Under these conditions, stable and repeatable operations were confirmed for both p- and n-type transistors. The PhC2-BQQDI transistor (blue line) showed an on/off ratio of approx. 10<sup>6</sup> along with an electron mobility of  $0.2 \pm 0.07$  cm<sup>2</sup> V s<sup>-1</sup>. On the other hand, the C8-BTBT transistor (red line) showed an even higher on/off ratio of approx. 10<sup>8</sup> and a hole mobility of  $1.2 \pm 0.2$  cm<sup>2</sup> V s<sup>-1</sup>. The threshold voltages ( $V_{th}$ ) of the respective transistors were 18 and -44 V.

These high carrier mobilities were also replicated in the performance of the HT, as shown in the transfer characteristics in Fig. 1(c). Here, a bias voltage ( $V_{DD}$ ) of -60 V was applied to the drain electrode, and the source electrode was

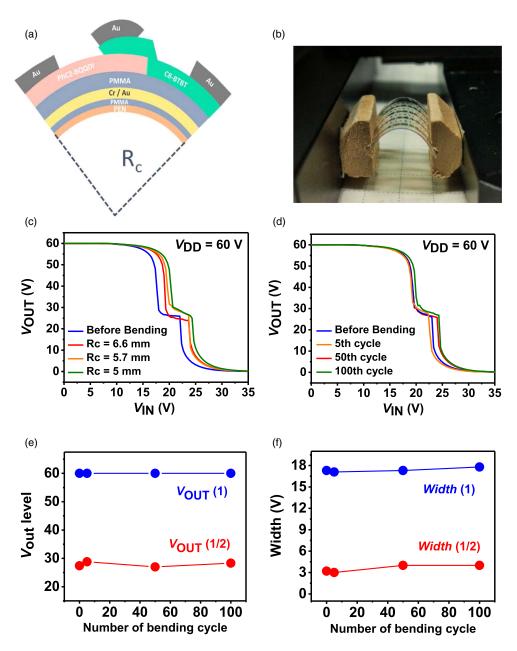

**Fig. 2.** (Color online) (a) Schematic illustration of the bent device structure;  $R_c$  represents the bending radius (b) Photograph of the setup for bending test (c) voltage transfer characteristics (VTCs) of the inverters as a function of bending radii (d) VTCs as a function of bending cycles at  $R_c = 5$  mm (e) Variations of logic state output voltage levels and (f) logic state widths as a function of bending cycle. [Before Bending -> Before bending; Number of bending cycle -> Number of bending cycles.]

grounded ( $V_{\text{GND}}$ ). The gate voltage ( $V_{\text{G}}$ ) was provided to the bottom gate electrode. Due to the favorable transport of electrons and holes across the junction, the HTs exhibited a high peak current ( $I_{\text{peak}}$ ) of 100 nA at a gate voltage ( $V_{\text{peak}}$ ) of -41 V followed by the NDT up to  $V_{\text{G}} = -44.5$  V. At higher  $V_{\text{G}}$  ranges, the continuous C8-BTBT layer resulted in a high on-current ( $I_{\text{on}}$ ) of 600 nA at  $V_{\text{G}} = -60$  V. As a result, an on/ off ratio of approx. 10<sup>6</sup> was yielded at an off-current ( $I_{\text{off}}$ ) of 0.3 pA at  $V_{\text{G}} = -6$  V.

The NDT characteristics and high on/off ratio thus obtained in the HTs enabled us to operate the ternary inverter as shown in Fig. 1(d). The logic circuit showed a complete  $V_{\text{OUT}}$  modulation from  $V_{\text{DD}}$  (60 V) to ground voltage (0 V), yielding three distinct and well-balanced logical states: logic 1 at  $V_{\text{OUT}}$  (1) =  $V_{\text{DD}}$  = 60 V, logic ½ at  $V_{\text{OUT}}$  (½) = 26 V ( $\approx V_{\text{DD}}/2$ ) and logic 0 at  $V_{\text{OUT}}$  = ground. Here, the  $V_{\text{OUT}}$  (½) level is determined mainly by the balance of the respective

channel resistances. The  $I_D$  and channel lengths are the key parameters. The value of  $I_D$  as a function of  $V_{IN}$  is shown in Fig. S2. Another important benefit of the inverter is the high DC voltage gain values shown in Fig. 1(e). The inverter was able to yield gain values as high as 29.5 V/V and 24 V/V at the first (logic 1 to logic  $\frac{1}{2}$  transition point) and second transition (logic  $\frac{1}{2}$  to logic 0 transition point) points, respectively. These are higher than for most previously reported ternary logic circuits.<sup>14,18,25</sup>

Next, we carried out cyclic bending tests to evaluate the mechanical flexibility and reliability of the ternary inverters. The bending direction is schematically illustrated in Fig. 2(a), where  $R_c$  represents the bending radius of the curvature. Figure 2(b) shows a photograph of the setup under bent conditions. First, the electrical characteristics of the devices were measured as a function of the bending radii. All the data were obtained in the flat form after the bending tests.

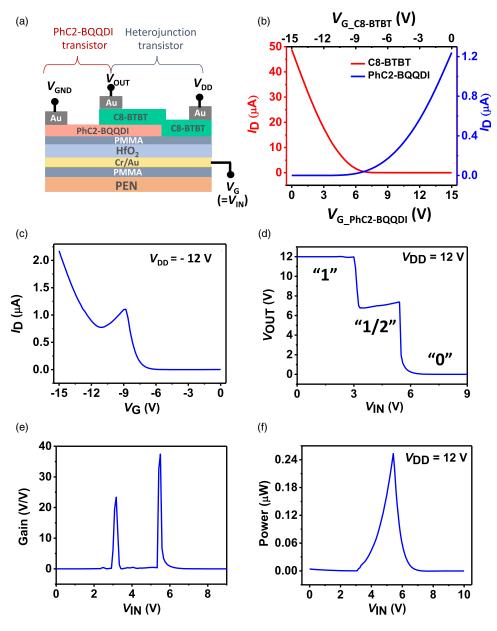

**Fig.3.** (Color online) (a) Schematic illustration of the ternary inverter with HfO<sub>2</sub> dielectric layer. (b) Transfer characteristics (at  $V_D = |12|$  V) of the C8-BTBT (red line) and PhC2-BQQDI (blue line) transistors. (c) Transfer curve of the heterojunction transistor at  $V_{DD} = -12$  V. (d) Voltage transfer characteristics of the ternary inverter at  $V_{DD} = 12$  V. (e) DC voltage gain and (e) static power consumption of the ternary inverters as a function of input voltage.

Although a slight shift in the voltage transfer curve (VTC) toward a higher  $V_{\rm IN}$  was observed at  $R_{\rm c} = 6.6$  mm, the voltage levels of the three logic states and logic 1/2 width remained close to constant, as shown in Fig. 2(c). This is because the bending induced a  $V_{\rm th}$  shift only in the C8-BTBT channel, whereas no variation was induced in the PhC2-BQQDI channel, as shown in the supporting information (Fig. S3). The VTCs clearly demonstrated ternary logic states even under the more stringent condition of  $R_c = 5$  mm. These results indicate that the devices can withstand applied mechanical strain, even at an  $R_c$  of 5 mm. This corresponds to a tensile strain ( $\varepsilon$ ) of 1.25%, which was calculated from  $\varepsilon = t/2R_c$ , where t is the thickness of the PEN substrate (125  $\mu$ m). The tolerance of the devices to repeated bending was then tested at  $R_c = 5$  mm. The VTCs in Fig. 2(d) were virtually unchanged, even after 100 bending cycles. The variation in the  $V_{OUT}$  levels and widths of the logic states are

plotted as a function of numbers of bending cycles in Figs. 2(e) and 2(f), respectively. The  $V_{OUT}$  levels and widths of logic 1 and logic  $\frac{1}{2}$  states are denoted as  $V_{OUT}$  (1), *Width* (1),  $V_{OUT}$  ( $\frac{1}{2}$ ) and *Width* ( $\frac{1}{2}$ ), respectively [see Fig. 1(e)].  $V_{OUT}$  (1) showed no variation with the bending cycle and remained constant at 60 V, whereas the  $V_{OUT}$  ( $\frac{1}{2}$ ) showed a marginal change of 2% after 100 cycles. For the logic state widths, both *Width* (1) and *Width* ( $\frac{1}{2}$ ) remained almost constant at 17.5 ± 0.3 V and 3.6 ± 0.4 V, respectively. These results clearly exhibit another merit of our devices, that is, their high mechanical bendability, which is necessary for flexible electronic applications.

Here, it should be noted that one challenge remained: the device requires a high driving voltage ( $V_{DD} = 60 \text{ V}$ ) for inverter operation. This problem was resolved by taking advantage of the high-*k* HfO<sub>2</sub> ( $k \approx 19$ ) dielectric layer.<sup>29)</sup> It is well known that high-*k* dielectric layers induce a high charge-

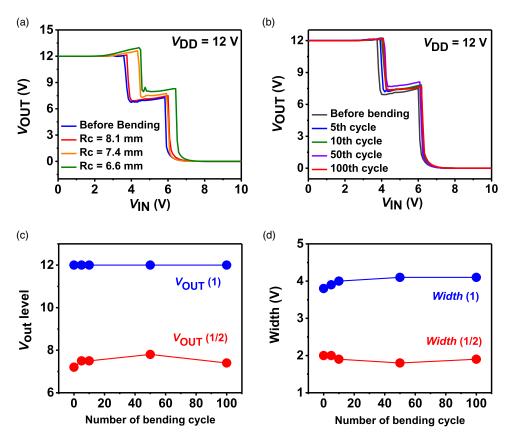

Fig. 4. (Color online) (a) Voltage transfer curves of the inverters as a function of bending radii (d) VTCs as a function of bending cycles at  $R_c = 8.1$  mm. Variations in (e) output voltage levels and (f) logic state widths as a function of bending cycle. [Before Bending -> Before bending; Number of bending cycle -> Number of bending cycles.]

carrier density at the dielectric/semiconductor interface and thus can effectively reduce the operation voltage of the transistors.<sup>30,31)</sup> A schematic illustration of the inverter configuration is shown in Fig. 3(a). Here, a 30 nm thick HfO<sub>2</sub> layer was deposited on top of the gate electrodes layer by atomic layer deposition using tetrakis(dimethylamino) hafnium (TDMAH) as the hafnium precursor and water as the oxygen source. A 10 nm thick PMMA layer was deposited on the HfO<sub>2</sub> coating as a surface treatment designed to passivate the interfacial carrier traps and to facilitate charge transport at the dielectric-semiconductor interface.<sup>30,32</sup>

Figure 3(b) shows the transfer curves of the PhC2-BQQDI (blue line) and C8-BTBT (red line) transistors with the HfO<sub>2</sub> dielectric layer. The threshold voltages  $(V_{th})$  of both transistors were effectively reduced to 6 V and -8 V, respectively. In response to the reduction of  $V_{\rm th}$ , the HT and ternary inverter attained low-voltage operation, as observed in Figs. 3(c) and 3(d), respectively. The HT showed a high peak current ( $I_{\text{peak}}$ ) of 1  $\mu$ A at  $V_{\text{G}} = V_{\text{Peak}} = -9$  V.  $I_{\text{on}}$  of  $2 \,\mu\text{A}$  was obtained at  $V_{\text{G}} = 15 \,\text{V}$ , yielding the on/off ratio of  $10^6$  ( $I_{off} = 3$  pA at  $V_G = -2.8$  V). Moreover, a wide NDT range from -9 to -11 V was realized under the drain bias voltage  $V_{\rm DD}$  of -12 V. Due to these superior electrical properties of the constituent transistors, the inverters also exhibited high performance, including full-swing operation well-balanced states: and ternary logic 1 at  $V_{\text{OUT}} = V_{\text{DD}} = 12 \text{ V}$ , logic <sup>1</sup>/<sub>2</sub> at  $V_{\text{OUT}} \approx V_{\text{DD}}/2 = 7 \text{ V}$  and logic 0 at  $V_{OUT}$  = ground. Interestingly, the DC gain values were further improved to 23.4 V/V and 37.5 V/V at  $V_{\rm IN} = 3.2$  V and 5.5 V, respectively, as shown in Fig. 3(e).

In addition to low-voltage operation, use of the HfO<sub>2</sub> layer afforded another advantage: lower static power consumption. The power consumption (*P*) of the inverter was calculated from  $P = (V_{DD} \times I_{GND})$  and is plotted as a function of  $V_{IN}$  in Fig. 3(f). The peak power consumption of the HfO<sub>2</sub>-based device was found to be only 240 nW, which is almost one order less than the maximum power consumption of the inverter with the PMMA dielectric layer (see Fig. S4 in the supporting information). These results clearly demonstrate the application potential of the HfO<sub>2</sub>-based organic MVLs in low-power ICs.

Finally, we examined the impact of substrate bending on HfO<sub>2</sub>-based inverters. Similar to PMMA-based devices, we carried out bending tests at different bending radii to determine the tolerance limit of the devices. As shown in Fig. 4(a), the inverter characteristics remained almost unchanged after an applied bending radius of 8.1 mm. However, the VTCs showed pronounced shifts towards higher  $V_{IN}$ along with a deformation in the  $V_{OUT}$  (1) on decreasing the  $R_{\rm c}$ , indicating that the devices can withstand bending down to a radius of 8.1 mm. The mechanical robustness of the devices was then tested by applying 100 bending cycles at  $R_{\rm c} = 8.1$  mm, as shown in Fig. 4(b). The VTCs of the inverters displayed very stable behavior in the cyclic bending test. Figures 4(c) and 4(d) respectively show the bending cycle-induced variation of  $V_{OUT}$  levels and the widths of the logic states. V<sub>OUT</sub> (1) was found to remain constant at 12 V, regardless of the numbers of bends, that is, full-swing operations were maintained. On the other hand,  $V_{OUT}$  (1/2) showed slight fluctuation with bending cycles with a maximum of an 8% change at the 50th bending. Width (1) and Width ( $\frac{1}{2}$ ) also showed negligible variation with bending cycles and remained constant at  $4 \pm 0.2$  V and  $1.9 \pm 0.1$  V, respectively, demonstrating the high reliability of the HfO<sub>2</sub> devices under moderate bending conditions.

In summary, we have developed organic ternary logic circuits on flexible PEN substrates. First, the inverters were fabricated using a PMMA dielectric layer to prioritize mechanical flexibility. The devices showed three distinct, well-balanced logic states with high voltage gain and fullswing operation. The most important advantage of the devices was their ability to tolerate a tensile strain of up to 1.25%. However, the devices required a supply voltage of 60 V for inverter operation. This drawback was tackled by taking advantage of the high-k HfO2 dielectric layer to investigate the potential for low-voltage operation. The HfO<sub>2</sub>-based inverter was operable at 12 V. The devices also proved very resistant to an applied tensile strain of up to 0.78%, and displayed stable operation after 100 bending cycles. Both devices exhibited their own merits and can, accordingly, be utilized in different potential applications. This work, therefore, paves a realistic path towards the development of flexible and low-power organic MVLs for next-generation conformable logic applications.

**Acknowledgments** This research was supported by the World Premier International Center (WPI) for Materials Nanoarchitectonics (MANA) of the National Institute for Materials Science (NIMS), Tsukuba, Japan, and JSPS Kakenhi grant numbers 19H00866 and 21F21052. The authors thank Dr. Takeo Minari for his technical support with handling flexible PEN substrates.

- ORCID iDs Ryoma Hayakawa D https://orcid.org/0000-0002-1442-

- 8230 Kaname Kanai 向 https://orcid.org/0000-0002-3952-

- 5491 Yutaka Wakayama (i) https://orcid.org/0000-0002-0801-8884

- 1) K. J. Baeg and J. Lee, Adv. Mater. Technol. 5, 2000071 (2020).

- K. S. Daeg and J. Ecc, Adv. Match. Technol. 3, 2000/1 (2020).

L. Cai, S. Zhang, J. Miao, Z. Yu, and C. Wang, ACS Nano 10, 11459

- (2016).

- 3) J. Shi et al., Adv. Mater. 32, 1901958 (2020).

- 4) Y. Lan et al., ACS Appl. Mater. Interfaces 12, 26145 (2020).

- W. Zeng, L. Shu, Q. Li, S. Chen, F. Wang, and X. M. Tao, Adv. Mater. 26, 5310 (2014).

- H. Zhu, E. S. Shin, A. Liu, D. Ji, Y. Xu, and Y. Y. Noh, Adv. Funct. Mater. 30, 1904588 (2020).

- 7) Y. Tang, X. Li, H. Lv, W. Wang, C. Zhi, and H. Li, InfoMat 2, 1109 (2020).

- E. Ragonese, M. Fattori, and E. Cantatore, IEEE Trans. Circuits Syst. II 68, 42 (2020).

- 9) S. E. Root, S. Savagatrup, A. D. Printz, D. Rodriquez, and D. J. Lipomi, Chem. Rev. 117, 6467 (2017).

- T. Sekitani, U. Zschieschang, H. Klauk, and T. Someya, Nat. Mater. 9, 1015 (2010).

- 11) Y. Choi, H. Kim, K. Sim, K. Park, C. Im, and S. Pyo, Org. Electron. 10, 1209 (2009).

- 12) G. Casula, S. Lai, L. Matino, F. Santoro, A. Bonfiglio, and P. Cosseddu, Adv. Electron. Mater. 6, 1901027 (2020).

- 13) S. B. Jo, J. Kang, and J. H. Cho, Adv. Sci. 8, 2004216 (2021).

- 14) M. Huang, S. Li, Z. Zhang, X. Xiong, X. Li, and Y. Wu, Nat. Nanotechnol. 12, 1148 (2017).

- 15) J. H. Lim et al., Adv. Funct. Mater. 29, 1905540 (2019).

- 16) H. Yoo and C. H. Kim, J. Mater. Chem. C 9, 4092 (2021).

- 17) J. Shim, S. H. Jo, M. Kim, Y. J. Song, J. Kim, and J. H. Park, ACS Nano 11, 6319 (2017).

- 18) A. Nourbakhsh, A. Zubair, M. S. Dresselhaus, and T. Palacios, Nano Lett. 16, 1359 (2016).

- 19) S. Seo et al., NPJ 2D Mater. Appl. 5, 1 (2021).

- 20) B. Kim, Adv. Electron. Mater. 6, 2000426 (2020).

- 21) S. L. Hurst, IEEE Trans. Comput. 12, 1160 (1984).

- 22) S. L. Hurst, Opt. Eng. 25, 250144 (1986).

- 23) B. Fresch, M. V. Klymenko, R. D. Levine, and F. Remacle, *Computational Matter* (Springer, Cham, 2018), p. 295.

- 24) K. Kobashi, R. Hayakawa, T. Chikyow, and Y. Wakayama, Nano Lett. 18, 4355 (2018).

- 25) H. Yoo, S. On, S. B. Lee, K. Cho, and J. J. Kim, Adv. Mater. 31, 1808265 (2019).

- 26) D. Panigrahi, R. Hayakawa, K. Fuchii, Y. Yamada, and Y. Wakayama, Adv. Electron. Mater. 7, 2000940 (2020).

- 27) T. Okamoto et al., Sci. Adv. 6, eaaz0632 (2020).

- 28) T. Izawa, E. Miyazaki, and K. Takimiya, Adv. Mater. 20, 3388 (2008).

- 29) Y. S. Lin, R. Puthenkovilakam, and J. P. Chang, Appl. Phys. Lett. 81, 2041 (2002).

- 30) T. H. Huang, K. C. Liu, Z. Pei, W. K. Lin, and S. T. Chang, Org. Electron. 12, 1527 (2011).

- 31) R. Ponce Ortiz, A. Facchetti, and T. J. Marks, Chem. Rev. 110, 205 (2010).

- 32) M. Held, S. P. Schießl, D. Miehler, F. Gannott, and J. Zaumseil, Appl. Phy. Lett. 107, 83 (2015).