# Dual-Gate Anti-Ambipolar Transistor with Van der Waals ReS<sub>2</sub>/WSe<sub>2</sub> Heterojunction for Reconfigurable Logic Operations

Yoshitaka Shingaya, Amir Zulkefli, Takuya Iwasaki, Ryoma Hayakawa, Shu Nakaharai, Kenji Watanabe, Takashi Taniguchi, and Yutaka Wakayama\*

A dual-gate anti-ambipolar transistor (AAT) with a two-dimensional  $\text{ReS}_2$ and  $\text{WSe}_2$  heterojunction is developed. The characteristic  $\Lambda$ -shaped transfer curves yielded by the bottom-gate voltage are effectively controlled by the top-gate voltage. This feature is applied to logic operations, with the bottomand top-gate voltages acting as two input signals and the drain current ( $I_d$ ) monitored as an output signal. Importantly, a single dual-gate AAT exhibits all the two-input logic operations (AND, OR, XOR, NAND, NOR, and XNOR) under optimized input voltages. Additionally, drain voltage ( $V_d$ )-induced switching between AND and OR logic operations is achieved. These features are advantageous for simplifying circuit design.

# **1. Introduction**

Beginning with the emergence of graphene,<sup>[1–3]</sup> the device applications of various two-dimensional (2D) layered materials, including transition metal dichalcogenides (TMDCs), have attracted much attention, and many related studies have been reported.<sup>[4–8]</sup> In particular, TMDCs can be utilized as transistor channels owing to their various band structures, and thus are expected to be utilized in a variety of functional devices. The 2D materials are layered compounds with atomically flat surfaces, in which each layer is stacked with weak van der Waals interaction. Therefore, various combinations of materials are available for forming heterojunctions without the lattice mismatch limitation. This characteristic is very useful in developing antiambipolar transistors (AATs). AATs have a unique structure:

D The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202200704.

© 2022 The Authors. Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### DOI: 10.1002/aelm.202200704

n- and p-type semiconductors are overlapped at the center of the transistor channel<sup>[9]</sup> to make direct contact with no depletion layer. There are numerous studies of AATs, respectively utilizing organic semiconductors,<sup>[10–12]</sup> 2D TMDCs,<sup>[13–16]</sup> and combinations of these materials.<sup>[17,18]</sup> The uniqueness of AATs can be ascribed to the  $\Lambda$ -shaped transfer curves. The  $I_d$  increases from a certain voltage, and then decreases with increasing gate bias voltage, a behavior similar to that of negative differential resistance (NDR). Although NDR devices have been expected to be key elements of logic circuits since the invention of the Esaki diode,<sup>[19]</sup> no practical device

has yet been developed, because cryogenic temperatures are necessary for device operation and the peek-to-valley ratio (PVR) is only about 30 at room temperature,<sup>[20]</sup> which is insufficient for practical applications. In contrast, AATs can achieve high PVRs of  $10^3-10^5$  even at room temperature.<sup>[17,21,22]</sup> Therefore, AATs are strong candidates for use in new NDR devices, and multi-valued logic circuits have, in fact, been developed by taking advantage of this feature.<sup>[11,23]</sup> The present study exploited the NDR property to enable two-input logic operations, through the construction of a dual-gate AAT with an ReS2/WSe2 heterojunction. An important feature of the study was that all the two-input logic operations (AND, OR, XOR, NAND, NOR, and XNOR) were demonstrated using a single dual-gate AAT owing to its reconfigurable characteristics. Conventionally, a large number of transistors are required for conventional CMOS-based logic circuit technology (e.g., 12 transistors for a complementary-type XOR gate). In contrast, the reconfigurable dual-gate AAT offers a novel device architecture for the simplification of logic circuits and improvement in integration density.

Reconfigurable field-effect transistors are electronic devices that can reversibly change their conduction modes between p-type and n-type.<sup>[24–27]</sup> Such operation is available by plural gate electrodes those are program (or polar) and control gates. The program gate is to change the conduction modes between n- and p-type, and the control gate is to switch the field effect transistor (FET) between on and off states. Importantly, the conduction mode conversion is induced by electrostatic doping, i.e., electrons or holes are injected into the transistor channel by external bias voltage and, therefore, the channel materials are intrinsic semiconductors. Various materials have been reported for transistor channels, such as carbon nanotubes (CNTs)<sup>[28]</sup> Si nanowires,<sup>[29,30]</sup> graphene,<sup>[31]</sup> and transition metal

Y. Shingaya, A. Zulkefli, T. Iwasaki, R. Hayakawa, S. Nakaharai, T. Taniguchi, Y. Wakayama International Center for Materials Nanoarchitectonics (WPI-MANA) National Institute for Materials Science (NIMS) 1-1 Namiki, Tsukuba 305-0044, Japan E-mail: wakayama.yutaka@nims.go.jp K. Watanabe Research Center for Functional Materials National Institute for Materials Science (NIMS) 1-1 Namiki, Tsukuba 305-0044, Japan

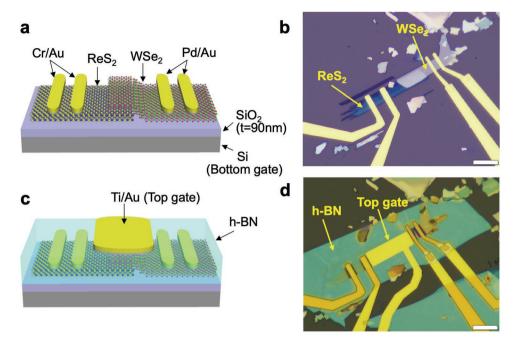

**Figure 1.** a) Schematic illustration and b) optical microscope image of a bottom-gate  $ReS_2/WSe_2$  AAT. Scale bar: 10  $\mu$ m. c) Schematic illustration and d) optical microscope image of the dual-gate  $ReS_2/WSe_2$  AAT. The h-BN thin film was used as an insulating layer for the top gate. Scale bar: 10  $\mu$ m.

dichalcogenides.<sup>[32]</sup> Although there have been many reports on logic operations using 2D materials,<sup>[33–36]</sup> in this study, we developed a new type of reconfigurable device based on the AAT. Here, the heterojunction with transition metal dichalcogenides plays crucial role to change the type of logic operation by optimizing the input bias voltages.

#### 2. Results and Discussions

The heterojunction was fabricated by using ReS<sub>2</sub> and WSe<sub>2</sub> as the n-type and p-type semiconductors, respectively. Figures 1a,b respectively show a schematic illustration and an optical microscope image of a bottom-gate AAT. Cr/Au (5/100 nm) and Pd/Au (20/80 nm) electrodes were connected to the ReS<sub>2</sub> and WSe<sub>2</sub> channels, respectively, to investigate the electrical properties of the individual ReS<sub>2</sub> and WSe<sub>2</sub> transistors and those of the AAT. The channel length and width were 21.0 and 4.9 µm, respectively. The length of the overlapping area was 10.0  $\mu$ m. The film thickness of the  $ReS_2$  and  $WSe_2$  was 4.8 nm (6 layers) and 10.0 nm (15 layers), respectively. Figure 1c shows a schematic illustration of a dual-gate AAT, with a hexagonal boron nitride (h-BN) film of 29.5 nm thickness covering the entire device and working as a top-gate dielectric layer. Then, a Ti/Au (5/100 nm) electrode was patterned as a top-gate electrode to cover the entire channel area. Figure 1d shows an optical microscope image of the prepared dual-gate AAT.

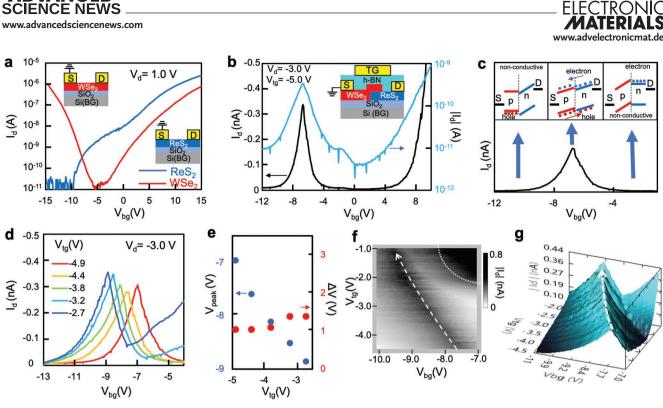

The transfer curves of the  $\text{ReS}_2$  (blue) and  $\text{WSe}_2$  (red) fieldeffect transistors (FETs) are shown in **Figure 2**a. Here, the  $\text{ReS}_2$  FET shows n-type characteristics, while the WSe<sub>2</sub> FET shows ambipolar characteristics. The threshold voltage of the  $\text{ReS}_2$  FET (-10.6 V) was lower than that of the WSe<sub>2</sub> FET of the p-type conduction (-6.8 V), which satisfied the condition for demonstrating anti-ambipolar characteristics. The field-effect mobilities were determined to be 8.4 and 6.5 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the ReS<sub>2</sub> and WSe<sub>2</sub> FETs, respectively. These comparable mobilities are advantageous for balancing the electron and hole transports.

Figure 2b shows the carrier transport characteristics of the ReS<sub>2</sub>/WSe<sub>2</sub> AAT driven by bottom-gate voltage (Vbg) at a fixed drain voltage ( $V_d$ ) of -3 V. The transfer curves are shown in linear (black) and log (blue) scales. A typical A-shaped curve with a peak at -6.7 V was observed in the  $V_{\rm bg}$  range from -4 to -12 V, and the sharp and symmetric curve indicated good balance between the electron and hole transports. It should be noted that  $I_d$  increased again above 4 V of  $V_{bg}$ . This was due to the ambipolar characteristics of the WSe<sub>2</sub> FET; both the ReS<sub>2</sub> and WSe<sub>2</sub> FETs were in the on state in this range. The gate-bias dependence of the energy-level alignments is shown in Figure 2c, to explain the origin of the A-shaped characteristics. In the range around  $V_{bg} = -12$  V, no electrical current was observed because the n-channel was non-conductive. Similarly, no electrical current was observed in the range around  $V_{\rm bg} = -2$  V because the p-channel was non-conductive. Both the n- and p-channels were in the on state only in the middle range from -4 to -12 V. As a result, a sharp increase and decrease in  $I_{\rm d}$  was induced, with monotonically increasing  $V_{\rm bg}$ , to yield the  $\Lambda$ -shaped curve.

Next, we examined the effect of the top-gate bias voltage ( $V_{tg}$ ) on the transfer curve. Figure 2d shows the variation in the transfer curve when the  $V_{tg}$  was applied from -4.9 V (red) to -2.7 V (dark blue). Figure 2e shows the  $V_{tg}$  dependence of the peak voltage ( $V_{peak}$ ) and peak width ( $\Delta V$ ). Here,  $\Delta V$  was defined as a peak width at  $|I_d| = 0.2$  nA. The  $V_{peak}$  exhibited clear dependence on the  $V_{tg}$ , shifting from -7.0 to -8.9 V. On the other hand,  $\Delta V$  around 1.1 V was almost constant throughout the whole  $V_{tg}$  range. These results indicate that the threshold voltage of

Figure 2. a) Transfer characteristics of the ReS2-FET (blue) and WSe2-FET (red). b) A-shaped transfer characteristics of the ReS2/WSe2 AAT. c) Energylevel alignments depending on gate bias voltage ( $V_{bg}$ ), and the  $\Lambda$ -shaped transfer curve. d)  $V_{tg}$  dependence of the transfer characteristics. e)  $V_{tg}$ dependence of the  $V_{\text{peak}}$  and peak width ( $\Delta V$ ) at  $|I_d| = 0.2$  nA. f) 2D and g) 3D plots of  $I_d$  against  $V_{\text{bg}}$  and  $V_{\text{tg}}$ . The  $V_{\text{peak}}$  was shifted by  $V_{\text{tg}}$ , as indicated by the dashed lines.

both the ReS<sub>2</sub> and WSe<sub>2</sub> FETs shifted equally depending on the V<sub>tg</sub>. Figures 2f,g respectively show two-dimensional and three-dimensional plots of  $I_d$  against  $V_{bg}$  and  $V_{tg}$ . The  $V_{peak}$  of the AAT shifted continuously, as indicated by the dashed lines. Additional intensive electrical current was observed around the upper right corner, as shown by the dotted arch in Figure 2f. This was also due to the ambipolar characteristics of the WSe<sub>2</sub> FET. These properties are significant for the realization of logic gate operations.

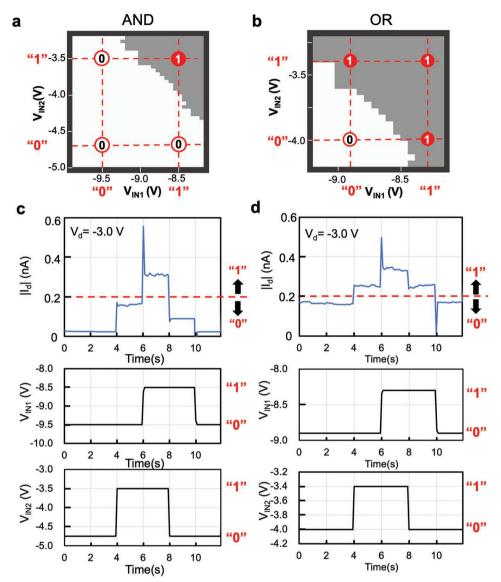

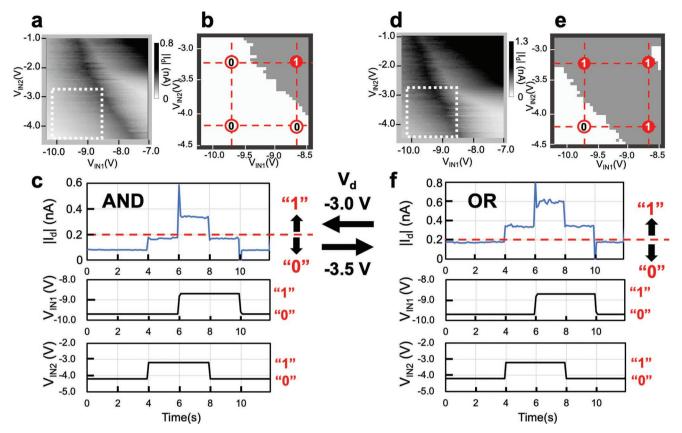

Based on these features of the dual-gate AAT, we developed two-input logic circuit operations. In Figure 3a,b, the bottomand top-gate voltages act as input 1 ( $V_{IN1}$ ) and input 2 ( $V_{IN2}$ ), respectively, and  $I_d$  was monitored as the output. The absolute values of the output current are mapped against input voltage 1 ( $V_{\rm IN1}$ ) and 2 ( $V_{\rm IN2}$ ), with the current binarized at a threshold current of 0.2 nA. Here, current greater than 0.2 nA (gray area) is defined as the on-state "1" of the output, and current less than 0.2 nA (white area) is defined as the off-state "0" of the output. Figure 3a demonstrates an AND logic operation, in which  $V_{IN1}$ of -9.5 and -8.5 V were defined as "0" and "1" for input 1, and  $V_{\rm IN2}$  of -4.7 and -3.5 V were defined as "0" and "1" for input 2, respectively. The output becomes on-state "1" only when both input 1 and input 2 are "1," indicating that the device operates as an AND circuit. Similarly, the OR operation was confirmed by changing the combination of input voltages as shown in Figure 3b. The logic operations driven by pulse voltage inputs are shown in Figure 3c,d. As shown in Figure 3c, the output current becomes larger than the threshold current of 0.2 nA only when both inputs are "1," which is the AND operation. Similarly, the OR operation was confirmed as shown in Figure 3d.

Here, it should be mentioned that spike noises were observed around 6 s in Figure 3c,d. We have conducted additional experiments to address noise margin issue by fabricating a new device. A h-BN layer was inserted at the SiO<sub>2</sub>/ReS<sub>2</sub>-WSe<sub>2</sub> interface (see Figure S1a-d, Supporting Information). AND and OR logic gates are shown in Figures S2a-d (Supporting Information) as typical device operations. Unlike Figure 3, no spike noise appeared in this device even when a pulse voltage was applied as shown in Figure S2c,d (Supporting Information) Thus, one can say that the spike noise appearing in Figure 3 is not an intrinsic problem because it can be completely eliminated by preparing high quality interface. The high quality interface is also effective in eliminating hysteresis in the transfer curves as shown in Figure S3 (Supporting Information).

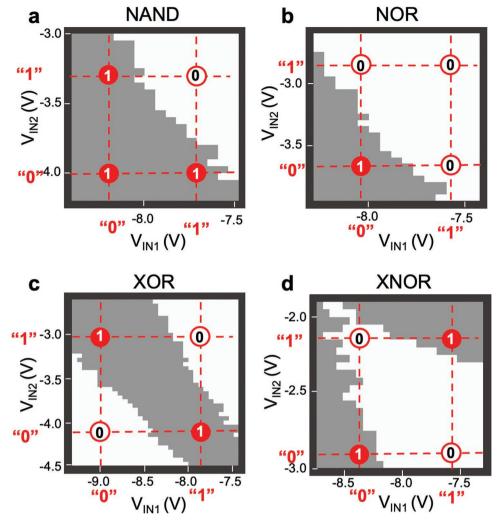

Importantly, the dual-gate AAT can enable AND and OR circuits independently, based on the input bias voltages, as demonstrated here. In a similar manner, other two-input logic operations (NAND, NOR, XOR, and XNOR) were enabled by optimizing the combination of the  $V_{IN1}$  and  $V_{IN2}$  voltages as input 1 and input 2, respectively, as shown in Figure 4a-d. The various logic operations were demonstrated simply by applying appropriate input voltages for the respective logic operations in a single device. This can be achieved only by the AAT because it allows the electrical current to flow only in the limited gate voltage ranges. It should be noted that a single current peak in the  $\Lambda$ -shaped curve cannot enable an XNOR circuit. However,  $I_{\rm d}$  increased again in the voltage range marked by the dotted arch in Figure 2f, producing another on-state "1" in the output, enabling XNOR operation, due to the ambipolar characteristics of the WSe2 FET (Figure 4d). In sum, all the two-input logic ADVANCED SCIENCE NEWS \_\_\_\_\_

**Figure 3.** Logic operations of the dual-gate AAT. The logic circuits were operated with the bottom-gate voltage ( $V_{IN1}$ ) as input 1, the top-gate voltage ( $V_{IN2}$ ) as input 2, and the  $I_d$  as output. 2D binarized mappings of  $|I_d|$  with a threshold current of 0.2 nA in an a) AND and b) OR circuit. Logic operations with pulse voltage input in a c) AND and d) OR circuit.

operations (AND, OR, XOR, NAND, NOR, and XNOR) were demonstrated. For the conventional logic operations, a number of transistors must be integrated (e.g., 4 transistors for NAND and NOR, and 12 transistors for XOR); however, the dual-gate AAT enabled all these operations in a single device architecture. Here, stable 2D mapping is necessary to guarantee the robustness of the logical input–output relationship. The stability of 2D mapping was investigated and the results was shown in Figure S4 (Supporting Information).

A further advantage of the AAT is its ability to operate at room temperature. Similar logic operations with a single device were reported by Majima et al.,<sup>[37]</sup> who developed single-electron transistors using gold particles, but a low-temperature environment was required for operation. By contrast, our device can work at room temperature, owing to the notable NDR of the AAT.

We also demonstrated another useful feature of the dualgate AAT: switchable logic operations based on drain voltage. As shown in Figure S5 (Supporting Information), the current peak of AAT shifts depending on V<sub>d</sub>. Therefore, by selecting the appropriate combination of  $V_d$ , it is possible to switch between different types of logic operations. Figure 5a-c shows experimental data for the AND operation: (a) wide-range 2D plots of  $|I_d|$  against  $V_{IN1}$  and  $V_{IN2}$ ; (b) binarized 2D plots of  $|I_d|$  with a threshold current of 0.2 nA, the voltage range of which was extracted from the dotted square in Figure 5a; and (c) pulse input voltage operation. These were obtained at a  $V_d$  of -3.0 V. Figure 5d-f shows similar data for the OR operation; the only difference being the  $V_d$  of -3.5 V, with the other parameters  $(V_{IN1}, V_{IN2}, and threshold current)$  identical to those of the AND operation. Even the small variation in  $V_d$ , however, from -3.0to -3.5 V, induced a drastic shift in the current peak, enabling ADVANCED SCIENCE NEWS \_\_\_\_\_

Figure 4. Various logic operations of the dual-gate AAT for a) NAND, b) NOR, c) XOR, and d) XNOR. These reconfigurable operations were enabled by appropriately optimizing the input voltages.

OR operation. These results indicate that variation in  $V_{\rm d}$  can be effectively used to switch logic operations.

It should be referred that there are still challenges in our present work for further improvements. First, respective logic gates were operated at arbitrary input voltages, although the input voltage must be fixed at a certain value in actual logic circuits. To address this issue, the  $V_{\text{peak}}$  of AAT must be adjusted to fix the drive voltage. A possible way to realize this is chemical doping into the 2D materials,<sup>[38–40]</sup> and then the desired logic operations can be performed at a constant input voltage. Second, the input voltages were rather high, nearly 10 V. This value can be lowered by reducing the thickness of the dielectric layer and by using high-k dielectric materials.

# 3. Conclusion

We developed a multifunctional logic gate circuit based on a dual-gate AAT. The  $\Lambda$ -shaped transfer curve and ambipolar property of the WSe<sub>2</sub> FET were key factors. These factors depended on the bottom-gate voltage and were modulated by

the top-gate voltage, enabling reconfigurable logic operations simply by optimizing the bias voltages. As a single device capable of performing all the two-input logic operations, the dual-gate AAT is expected to contribute to the simplification of circuit design and improvement in integration density.

# 4. Experimental Section

Device Fabrication: The ReS<sub>2</sub>/WSe<sub>2</sub> heterojunction was fabricated using a bubble-free dry transfer technique.<sup>[41–43]</sup> The home-built transfer equipment consisted of an optical microscope (BX53M, Olympus Co.), manipulator, and heater. First, thin films of ReS<sub>2</sub> and WSe<sub>2</sub> were prepared from commercial bulk crystals (HQ Graphene) by the mechanical exfoliation method, using adhesive tape on highly doped Si substrate with a 90-nm thick SiO<sub>2</sub> layer. These films acted as a bottom gate and gate dielectric layer, respectively. TMDC flakes of a few nanometers in thickness were selected using optical microscopy, and the exact thickness, width, and length of the flakes were measured using an atomic force microscope (AFM). A combination of ReS<sub>2</sub> and WSe<sub>2</sub> flake was stacked on the ReS<sub>2</sub> flake using the dry transfer method. A pair of Cr/Au (5/100 nm) electrodes, and another pair of Pd/Au

**Figure 5.** Switching between AND and OR operation by changing the drain voltage. a–c) AND operation at  $V_d$  = –3.0 V. d–f) OR operation at  $V_d$  = –3.5 V. Wide-range 2D plots of  $|I_d|$  (a, d). Binarized 2D plots of  $|I_d|$  extracted from the dotted squares in (a) and (d) (b, e). Logic operations with pulse voltage input (c, f).

(20/80 nm) electrodes, were put in contact with the ReS<sub>2</sub> and WSe<sub>2</sub> layers, respectively, using an electron beam evaporation and lithographic process. The Cr and Pd thin films were inserted to reduce the Schottky barrier in the contact area.<sup>[44,45]</sup> Subsequently, a h-BN film was stacked as the top-gate insulator, covering the entire device. Finally, a Ti/Au (5/100 nm) film covered the entire channel as the top gate. A Ti thin layer was inserted at the interface, for better mechanical bonding with the h-BN surface.

*Device Characterization*: The electrical characteristics of the device were measured in a vacuum (40 Pa) at room temperature using a probe station. The current–voltage and current–time characteristics were measured using source-measurement units (Agilent, B2912A, B2901A). An AFM (MFP-3D, Oxford Instruments) was used to measure the dimensions of the TMDC flakes, check the cleanliness, and remove the resist residues.

# **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

# Acknowledgements

This work was supported by the World Premier International Center (WPI) for Materials Nanoarchitectonics (MANA) of the National Institute for Materials Science (NIMS), Tsukuba, Japan, and JSPS Kakenhi grant numbers 19H00866 and 21F21052. A part of this study was supported by the NIMS Nanofabrication Platform as a program of the "Nanotechnology Platform" of the Ministry of Education, Culture, Sports, Science, and Technology (MEXT), Japan.

# **Conflict of Interest**

The authors declare no conflict of interest.

# **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Keywords**

2D materials, anti-ambipolar transistors, reconfigurable logic circuits,  $\mathsf{ReS}_2,\mathsf{WSe}_2$

Received: June 23, 2022 Revised: August 8, 2022 Published online:

K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, A. A. Firsov, *Science* 2004, *306*, 666.

<sup>[2]</sup> Y. Zhang, Y. W. Tan, H. L. Stormer, P. Kim, Nature 2005, 438, 201.

#### **ADVANCED** SCIENCE NEWS

www.advancedsciencenews.com

- [3] A. K. Geim, K. S. Novoselov, Nat. Mater. 2007, 6, 183.

- [4] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, Nat. Nanotechnol. 2011, 6, 147.

- [5] A. K. Geim, I. V. Grigorieva, Nature 2013, 499, 419.

- [6] H. Liu, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tomanek, P. D. Ye, ACS Nano 2014, 8, 4033.

- [7] A. Zulkefli, B. Mukherjee, R. Sahara, R. Hayakawa, T. Iwasaki, Y. Wakayama, S. Nakaharai, ACS Appl. Mater. Interfaces 2021, 13, 43030.

- [8] H. S. Song, S. L. Li, L. Gao, Y. Xu, K. Ueno, J. Tang, Y. B. Cheng, K. Tsukagoshi, *Nanoscale* **2013**, *5*, 9666.

- [9] Y. Wakayama, R. Hayakawa, Adv. Funct. Mater. 2019, 30, 1903724.

- [10] K. Kobashi, R. Hayakawa, T. Chikyow, Y. Wakayama, ACS Appl. Mater. Interfaces 2018, 10, 2762.

- [11] K. Kobashi, R. Hayakawa, T. Chikyow, Y. Wakayama, Nano Lett. 2018, 18, 4355.

- [12] K. Kobashi, R. Hayakawa, T. Chikyow, Y. Wakayama, J. Phys. Chem. C 2018, 122, 6943.

- [13] Y. Li, Y. Wang, L. Huang, X. Wang, X. Li, H.-X. Deng, Z. Wei, J. Li, ACS Appl. Mater. Interfaces 2016, 8, 15574.

- [14] C. R. Paul Inbaraj, R. J. Mathew, R. K. Ulaganathan, R. Sankar, M. Kataria, H. Y. Lin, Y. T. Chen, M. Hofmann, C. H. Lee, Y. F. Chen, ACS Nano 2021, 15, 8686.

- [15] T. Roy, M. Tosun, X. Cao, H. Fang, D.-H. Lien, P. Zhao, Y.-Z. Chen, Y.-L. Chueh, J. Guo, A. Javey, ACS Nano 2015, 9, 2071.

- [16] V. K. Sangwan, M. E. Beck, A. Henning, J. Luo, H. Bergeron, J. Kang, I. Balla, H. Inbar, L. J. Lauhon, M. C. Hersam, *Nano Lett.* 2018, 18, 1421.

- [17] C. J. Park, H. J. Park, J. Y. Lee, J. Kim, C. H. Lee, J. Joo, ACS Appl. Mater. Interfaces 2018, 10, 29848.

- [18] D. Jariwala, S. L. Howell, K. S. Chen, J. Kang, V. K. Sangwan, S. A. Filippone, R. Turrisi, T. J. Marks, L. J. Lauhon, M. C. Hersam, *Nano Lett.* **2016**, *16*, 497.

- [19] L. Esaki, Phys. Rev. 1958, 109, 603.

- [20] T. P. E. Broekaert, W. Lee, C. G. Fonstad, Appl. Phys. Lett. 1988, 53, 1545.

- [21] K. Kobashi, R. Hayakawa, T. Chikyow, Y. Wakayama, Adv. Electron. Mater. 2017, 3, 1700106.

- [22] Y. Wang, W.-X. Zhou, L. Huang, C. Xia, L.-M. Tang, H.-X. Deng, Y. Li, K.-Q. Chen, J. Li, Z. Wei, 2D Mater. 2017, 4, 025097.

- [23] J. Shim, S. Oh, D. H. Kang, S. H. Jo, M. H. Ali, W. Y. Choi, K. Heo, J. Jeon, S. Lee, M. Kim, Y. J. Song, J. H. Park, *Nat. Commun.* 2016, 7, 13413.

- [24] T. Mikolajick, A. Heinzig, J. Trommer, T. Baldauf, W. M. Weber, Semicond. Sci. Technol. 2017, 32, 043001.

- [25] T. Mikolajick, G. Galderisi, M. Simon, S. Rai, A. Kumar, A. Heinzig, W. M. Weber, J. Trommer, *Solid-State Electron*. **2021**, *186*, 108036.

- [26] G. V. Resta, Y. Balaji, D. Lin, I. P. Radu, F. Catthoor, P. E. Gaillardon, G. De Micheli, ACS Nano 2018, 12, 7039.

- [27] C. Pan, C. Y. Wang, S. J. Liang, Y. Wang, T. J. Cao, P. F. Wang, C. Wang, S. Wang, B. Cheng, A. Y. Gao, E. F. Liu, K. Watanabe, T. Taniguchi, F. Miao, *Nat. Electron.* **2020**, *3*, 383.

- [28] Y.-M. Lin, J. Appenzeller, P. Avouris, Electron Devices Meeting, 2004. IEDM Technical Digest. IEEE International, Dec. 2004, p. 687.

- [29] A. Heinzig, S. Slesazeck, F. Kreupl, T. Mikolajick, W. M. Weber, *Nano Lett.* 2012, 12, 119.

- [30] A. Heinzig, T. Mikolajick, J. Trommer, D. Grimm, W. M. Weber, *Nano Lett.* 2013, 13, 4176.

- [31] S. Nakaharai, T. Iijima, S. Ogawa, S. Suzuki, K. Tsukagoshi, S. Sato, N. Yokoyama, *Electron Devices Meeting (IEDM)*, 2012 IEEE International, Dec. 2012, 4.2.1.

- [32] S. Nakaharai, M. Yamamoto, K. Ueno, Y.-F. Lin, S.-L. Li, K. Tsukagoshi, ACS Nano 2015, 9, 5976.

- [33] D. Li, B. Wang, M. Chen, J. Zhou, Z. Zhang, Small 2017, 13, 1603726.

- [34] S. Wang, X. Pan, L. Lyu, C. Y. Wang, P. Wang, C. Pan, Y. Yang, C. Wang, J. Shi, B. Cheng, W. Yu, S. J. Liang, F. Miao, ACS Nano 2022, 16, 4528.

- [35] H. W. Chen, X. Y. Xue, C. S. Liu, J. B. Fang, Z. Wang, J. L. Wang, D. W. Zhang, W. D. Hu, P. Zhou, *Nat. Electron.* **2021**, *4*, 399.

- [36] M. E. Beck, A. Shylendra, V. K. Sangwan, S. Guo, W. A. Gaviria Rojas, H. Yoo, H. Bergeron, K. Su, A. R. Trivedi, M. C. Hersam, *Nat. Commun.* 2020, *11*, 1565.

- [37] K. Maeda, N. Okabayashi, S. Kano, S. Takeshita, D. Tanaka, M. Sakamoto, T. Teranishi, Y. Majima, ACS Nano 2012, 6, 2798.

- [38] H. Fang, S. Chuang, T. C. Chang, K. Takei, T. Takahashi, A. Javey, Nano Lett. 2012, 12, 3788.

- [39] H. Fang, M. Tosun, G. Seol, T. C. Chang, K. Takei, J. Guo, A. Javey, Nano Lett. 2013, 13, 1991.

- [40] L. Yu, A. Zubair, E. J. Santos, X. Zhang, Y. Lin, Y. Zhang, T. Palacios, Nano Lett. 2015, 15, 4928.

- [41] T. Iwasaki, K. Endo, E. Watanabe, D. Tsuya, Y. Morita, S. Nakaharai, Y. Noguchi, Y. Wakayama, K. Watanabe, T. Taniguchi, S. Moriyama, ACS Appl. Mater. Interfaces 2020, 12, 8533.

- [42] L. Wang, I. Meric, P. Y. Huang, Q. Gao, Y. Gao, H. Tran, T. Taniguchi, K. Watanabe, L. M. Campos, D. A. Muller, J. Guo, P. Kim, J. Hone, K. L. Shepard, C. R. Dean, *Science* **2013**, *342*, 614.

- [43] F. Pizzocchero, L. Gammelgaard, B. S. Jessen, J. M. Caridad, L. Wang, J. Hone, P. Boggild, T. J. Booth, *Nat. Commun.* 2016, *7*, 11894.

- [44] S. Das, J. Appenzeller, Appl. Phys. Lett. 2013, 103, 103501.

- [45] S. Das, M. Dubey, A. Roelofs, Appl. Phys. Lett. 2014, 105, 083511.