# First Demonstration of 25-nm Quad Interface p-MTJ Device With Low Resistance-Area Product MgO and Ten Years Retention for High Reliable STT-MRAM

K. Nishioka<sup>®</sup>, S. Miura<sup>®</sup>, H. Honjo<sup>®</sup>, H. Inoue, T. Watanabe, T. Nasuno, H. Naganuma<sup>®</sup>, T. V. A. Nguyen<sup>®</sup>, *Member, IEEE*, Y. Noguchi, M. Yasuhira, S. Ikeda<sup>®</sup>, and T. Endoh<sup>®</sup>, *Senior Member, IEEE*

Abstract—We successfully developed 25-nm quad CoFeB/MgO-interfaces perpendicular magnetic tunnel junction (quad-MTJ) with enough thermal stability. To fabricate the quad-MTJ, a physical vapor deposition (PVD) process for depositing novel free layer and low resistancearea (*RA*) product MgO layer and low-damage fabrication processes were developed. The developed quad-MTJ technology and advanced process bring better tunnel magneto resistance (TMR) ratio and *RA* to quad-MTJ than those of double-interface MTJ (double-MTJ), even though quad-MTJ

Manuscript received November 8, 2020; revised January 2, 2021, February 24, 2021, and April 12, 2021; accepted April 14, 2021. Date of publication May 3, 2021; date of current version May 21, 2021. This work was supported in part by the Center for Science and Innovation in Spintronics (CIES) Consortium, in part by the CIES's Industrial Affiliation on Spin-Transfer-Torque Magnetoresistive Random Access Memory (STT-MRAM) Program, in part by the Japan Science and Technology Agency-Program on Open Innovation Platform with Enterprises, Research Institute and Academia (JST-OPERA) Program under Grant JPMJOP1611, and in part by Cabinet Office – Cross-Ministerial Strategic Innovation Promotion Program (CAO-SIP). The review of this article was arranged by Editor J. Kang. (*Corresponding author: K. Nishioka.*)

K. Nishioka, S. Miura, H. Honjo, H. Inoue, T. Watanabe, T. Nasuno, Y. Noguchi, and M. Yasuhira are with the Center for Innovative Integrated Electronic Systems, Tohoku University, Sendai 980-8572, Japan.

H. Naganuma and T. V. A. Nguyen are with the Center for Innovative Integrated Electronic Systems, Tohoku University, Sendai 980-8572, Japan, also with the Center for Science and Innovation in Spintronics, Tohoku University, Sendai 980-8577, Japan, and also with the Center for Spintronics Research Network, Tohoku University, Sendai 980-8577, Japan (e-mail: hiroshi.naganuma.c3@tohoku.ac.jp).

S. Ikeda is with the Center for Innovative Integrated Electronic Systems, Tohoku University, Sendai 980-8572, Japan, also with the Center for Science and Innovation in Spintronics, Tohoku University, Sendai 980-8577, Japan, also with the Center for Spintronics Research Network, Tohoku University, Sendai 980-8577, Japan, and also with the Research Institute of Electrical Communication, Tohoku University, Sendai 980-8577, Japan.

T. Endoh is with the Center for Innovative Integrated Electronic Systems, Tohoku University, Sendai 980-8572, Japan, also with the Center for Science and Innovation in Spintronics, Tohoku University, Sendai 980-8577, Japan, also with the Center for Spintronics Research Network, Tohoku University, Sendai 980-8577, Japan, also with the Research Institute of Electrical Communication, Tohoku University, Sendai 980-8577, Japan, and also with the Graduate School of Engineering, Tohoku University, Sendai 980-8579, Japan (e-mail: tetsuo.endoh@cies.tohoku.ac.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2021.3074103.

Digital Object Identifier 10.1109/TED.2021.3074103

has an additional MgO layer. Scaling down the MTJ size to 25 nm, we demonstrated the advantages of quad-MTJ compared with double-MTJ as follows: 1) two times larger thermal stability factor ( $\Delta$ ), which results in over ten years retention; 2) superiority of large  $\Delta$  in the measuring temperature range up to 200 °C; 3) ~1.5 times higher write efficiency; 4) lower write current at short write pulse regions at less than 100 ns; and e) excellent endurance of over 10<sup>11</sup> thanks to higher write efficiency, which results from the reduced voltage owing to low *RA* and the low damage integration process technology. As a result, the developed quad-MTJ technologies will open the way for the realization of high-density STT-MRAM with low power, high speed, high reliability, and excellent scalability down to 2× nm node.

Index Terms—Interfacial anisotropy type magnetic tunnel junction (MTJ), low resistance-area (*RA*) product MGO, quad interface, spin-transfer-torque magnetoresistive random access memory (STT-MRAM), thermal stability factor.

### I. INTRODUCTION

THE spin-transfer torque [1], [2] magnetic random access memory (STT-MRAM) [3], [4] has been intensively researched and developed by many LSI companies and academic institutions because of its promising candidature as a low-power, high-performance memory in IoT, edge-AI, automobile applications [5], [6]. With the use of CoFeB/MgOinterface perpendicular magnetic tunneling junctions (p-MTJs) [7], the industrial application of STT-MRAM rapidly progressed [8]-[15], and major LSI companies started the mass production of STT-MRAM. However, for further expansion and promotion of its application areas and market, STT-MRAM must be further scaled. Although the double CoFeB/MgO-interface MTJ (double-MTJ) has become the de facto standard in current STT-MRAM technology [16], scaling issues still exist because a large enough thermal stability for nonvolatile memory was not obtained in the MTJ size of less than 30 nm.

To overcome this issue, we proposed a quad CoFeB/MgO-interface MTJ (quad-MTJ) structure [17], [18] and demonstrated its performance down to 33 nm [19]. Although the quad-MTJ has some scaling merits over the conventional double-MTJ [20], [21], its performance down to  $2 \times$  nm has

0018-9383 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

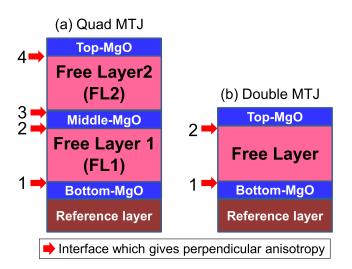

Fig. 1. Design concept of (a) quad CoFeB/MgO interface MTJ and (b) double CoFeB/MgO-interface MTJ. A larger number of the interface in the quad MTJ enables thicker free layer, resulting in high thermal stability [10].

not yet been demonstrated and its technologies have not yet been developed. Furthermore, the read and write properties with slight temperature dependence have been issues for practical usage. As the MTJ size becomes smaller, the influence of the damage regions at the MTJ side-wall becomes more critical [22]. To maintain the intrinsic performance of the quad-MTJ stack with  $2 \times$ -nm, a low damage MTJ fabrication process is essential.

For scaling down the MTJ, it must have a high thermal stability factor ( $\Delta$ ), high tunnel magnetoresistance (TMR) ratio, and low resistance, simultaneously. Fig. 1 depicts the design concept of quad- and double-MTJs [20]. Quad-MTJ comprises four CoFeB/MgO interfaces; this is twice the number of those in a conventional double-MTJ. This enables a thicker free layer because perpendicular anisotropy originates from the interface. Free Layer1 (FL1) and Free Layer2 (FL2) are ferromagnetically coupled through the middle MgO to increase the effective free layer volume, thus increase the thermal stability of the free layer. Materials of FL 1 and FL 2 are also important to improve high-temperature properties. Thermal tolerance of 400 °C is also required for CMOS back-endof-line process compatibility. To satisfy these requirements, we developed the fabrication processes of MgO and free layers for  $2 \times$ -nm quad-MTJ.

# II. ADVANCED PVD PROCESS FOR 2×-nm QUAD-MTJ

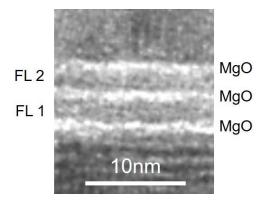

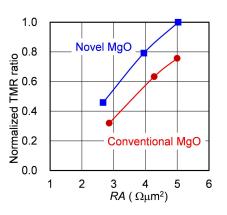

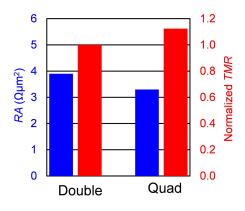

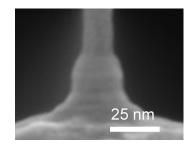

Fig. 2 shows the cross-sectional transmission electron microscopy (TEM) photography of quad-MTJ stack structure. Smooth interfaces of MgO layers were obtained by our advanced physical vapor deposition (PVD) processes. Figs. 3 and 4 show comparisons of transport properties of quad- and double-MTJs in the blanket film. The blanket MTJs were measured by the current-in-plane-tunneling (CIPT) method [23]. The TMR ratio of the developed quad-MTJ improved by over 20% owing to the novel MgO deposition process even in the *RA* range of less than 3  $\Omega \mu m^2$  (Fig. 3). Quad-MTJ achieved a high TMR ratio at a low *RA* (Fig. 4) despite a larger number

Fig. 2. Cross-sectional TEM photograph of quad-MTJ with advanced PVD process. A clear stack structure with three MgO layers and two free layers is obviously confirmed by our developed PVD process.

Fig. 3. Improvement of TMR ratio as a function of *RA* for the quad-MTJ in the blanket film. TMR ratio for the quad-MTJ was improved in comparison with quad-MTJ with conventional process owing to novel MgO deposition process.

Fig. 4. Improvement of TMR ratio in blanket film by developing the free layers and MgO barrier. Quad-MTJ has a larger TMR ratio at lower *RA* product by free layer material development.

of MgO layers through the development of the free layers and MgO layers. In addition, as a result, a high TMR and a low *RA* were simultaneously realized in the quad-MTJ.

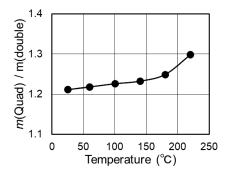

Fig. 5 shows the comparison of temperature (*T*) dependence of magnetization (magnetic moment per volume: *m*) for the quad-MTJ normalized by that of the double-MTJ. By a novel free layer development, the quad-MTJ's magnetization normalized by the double-MTJ increases with increasing temperature. This leads to a larger  $\Delta$  at RT and even larger  $\Delta$  at high

Fig. 5. Comparison of temperature (7) dependence on magnetization (*m*) of the quad-MTJ normalized by that of the double MTJ. In the quad-MTJ, *T* dependence of *m* was improved at higher temperature ( $\sim$ 225 °C) considerably comparing with double-MTJ.

Fig. 6. SEM photograph of 25-nm quad MTJ fabricated through our developed low-damage process. A clear stack structure and etching profile were observed in the MTJ.

temperature in the quad-MTJ compared with the double-MTJ as mentioned later. This is probably due to the temperature dependence of  $\Delta$  (i.e., magnetic anisotropy) is related to the temperature dependence of magnetization (*m*).

# III. PERFORMANCES OF 25-nm QUAD-MTJ

## A. Fabrication of 25-nm-Quad-MTJ

By applying the developed advanced process, 25-nm quad-MTJ is successfully fabricated as shown in Fig. 6. The MTJ stacks were deposited using a 300-mm dc/RF magnetron sputtering system and annealed at 400 °C for 1 h after deposition. The stacks were patterned into circular MTJs through electron beam lithography and developed pattern etching process, followed by deposition of the SiN protective layer and electrode wiring.

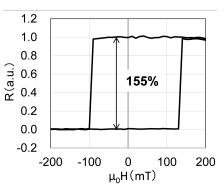

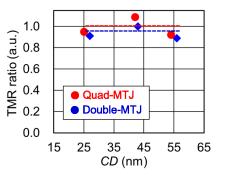

#### B. TMR Ratio Dependence on MTJ Size

As shown in Fig. 7, a high TMR ratio of 155% was obtained for the quad-MTJ. Fig. 8 shows the TMR ratio as a function of junction critical dimension (CD) of the quad- and double-MTJs. By developing the novel MgO layer and low-damage process, the TMR ratio of the quad-MTJ was maintained down to 25 nm, which is slightly larger than the double-MTJ for all CD size regions.

## C. $\triangle$ and $I_{C0}$ Dependence on MTJ Size

$\Delta$  and intrinsic critical write current ( $I_{C0}$ ) were evaluated from the switching probability of the write error rate (WER)

Fig. 7. Typical R-H loop of fabricated 25-nm quad-MTJ. We realized bistable magnetic switching with almost zero-shift magnetic field. TMR ratio shows 155%.

Fig. 8. CD dependence of TMR ratio of the quad- and double-MTJs. TMR ratio of quad-MTJ is almost constant with a decrease in the CD and is slightly larger than those of double-MTJ in all CD ranges.

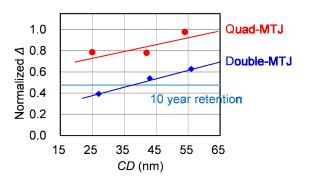

Fig. 9. Normalized thermal stability factor ( $\Delta$ ) at room temperature as a function of junction CD for the quad- and double-MTJs.  $\Delta$  of the quad-MTJ is almost 1.5–2.0 times larger than that of double-MTJ.  $\Delta$  of quad-MTJ exceeded those of Ten years' array-data retention ( $\Delta = 56$ ) with 1-ppm error.

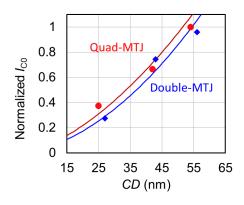

with a pulse width of 1  $\mu$ s. Fig. 9 shows the CD dependence of  $\Delta$  for the quad- and double-MTJs. By developing the quad-MTJ technology,  $\Delta$  can be enhanced by a factor of about 1.5–2. Quad-MTJs achieved ten years of retention when CD was down to 25 nm by using a developed low-damage fabrication process. Furthermore, by extrapolating from the measurement results based on the macrospin model, it is expected that ten years of retention will be achieved for the quad-MTJ down to 10 nm. Fig. 10 shows normalized  $I_{C0}$  as a function of CD. The  $I_{C0}$  was normalized by 55 nm in CD. It was revealed that there is no significant difference in the

Fig. 10. CD dependence of critical write current ( $I_{C0}$ ) for the quad- and double-MTJs. The quad-MTJ showed almost same  $I_{C0}$  as the double-MTJ in all CD regions.

Fig. 11. (a) Write efficiency  $(\Delta/I_{C0})$  as a function of junction CD for the quad- and double-MTJs. (b)  $\Delta/I_{C0}$  of the quad-MTJ was  $\sim$ 1.5 times larger than that of the double-MTJ.

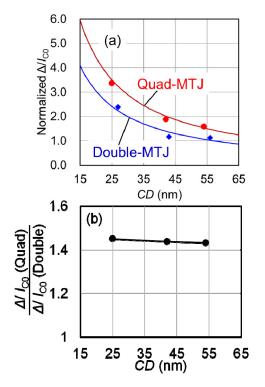

two types of MTJ (quad- and double-MTJs). The relatively weak magnetic coupling between FL1 and FL2 may give a magnetization process that is out of sync with FL1 and FL2 during writing, resulting in a relatively small write current despite maintaining high thermal stability [24], [25]. Therefore, as shown in Fig. 11(a), write efficiency ( $\Delta/I_{C0}$ ) in the quad-MTJs is higher than those of the double-MTJ even in the CD range of 2× nm. The write efficiency ( $\Delta/I_{C0}$ ) in the quad-MTJ and the double-MTJ is about 1.5 in the measured CD range from 2× nm to 5× nm [Fig. 11(b)].

## D. $\triangle$ Dependence on Temperature

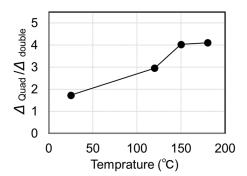

Fig. 12 shows the temperature dependence of the ratio of thermal stability factor for the quad-MTJ and the double-MTJ ( $\Delta_{\text{Ouad}}/\Delta_{\text{Double}}$ ). At R.T. (25 °C),  $\Delta$  of the 25-nm quad-MTJ

Fig. 12. Temperature dependence of relative thermal stability factor  $(\Delta_{Quad}/\Delta_{Double})$  in the 25-nm quad-MTJ and the 27-nm double-MTJ. The quad-MTJ showed high performance of thermal stability from 25 °C (R.T.) to 180 °C.

was 1.7 times higher than that of the double-MTJ at almost the same CD and maintains its superiority even when the temperature increases. In addition, the  $\Delta_{Quad}/\Delta_{Double}$  ratio achieved over 4 at over 150 °C, which means  $\Delta_{Double}$  decreases much more drastically than  $\Delta_{Quad}$  with the increase of temperature. That is, quad-MTJ has an advantage even in a high-temperature environment compared to double-MTJ. The reason why the  $\Delta_{Quad}/\Delta_{Double}$  became larger on the hightemperature side is considered to relate with the improvement of the temperature dependence of m(Quad)/m(Double) as shown in Fig. 5, because  $\Delta$  is proportional to  $M_s$ , and free layer is thicker in quad-MTJ.

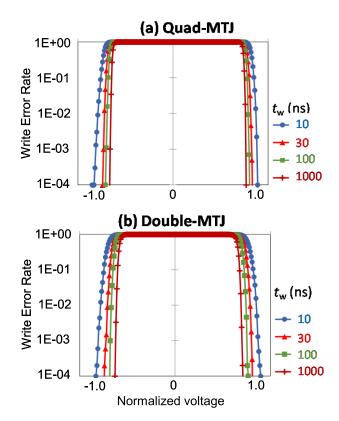

## E. Write Error Rate

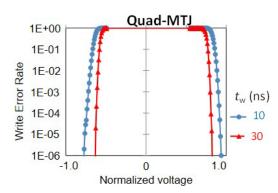

The write voltage dependence of WER was evaluated for the 25-nm quad-MTJ and the 27-nm double-MTJ (Fig. 13). In comparison with the double-MTJ, the quad-MTJ has a sharper WER curve, because the  $\Delta$  of the quad-MTJ is larger than that of the double-MTJ [19] and a high TMR ratio of quad-MTJ has high spin transfer efficiency. Furthermore, the quad-MTJ has a better slope of the WER shape than the double-MTJ until high-speed writing of 10 ns. The WER was measured down to  $10^{-6}$  with  $t_w(s)$  of 10 and 30 ns for the quad MTJ, and it showed that almost no change from the tendency up to  $10^{-4}$  [Fig. 14]. That is, the quad-MTJ can suppress the write voltage at a higher speed write operation compared to the double-MTJ.

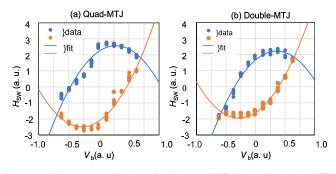

## F. Switching Field Versus Voltage

Fig. 15 shows the switching field  $(H_{sw})$  dependence of bias voltage  $(V_b)$  for the quad-MTJ and the double-MTJ. Fittings were performed with quadratic functions [26]. Coefficients of  $V^2$  are thought to correlate with self-heating effects. Coefficients of  $V^2$  normalized by resistance-area (*RA*) product for quad-MTJs are nearly the same as those for double-MTJs. These results suggest the self-heating effects of the quad-MTJ are similar to those of the double-MTJs.

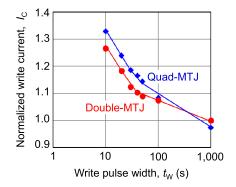

#### G. Write Speed Versus Write Current

Fig. 16 shows the dependence of the write current  $(I_C)$  on the write pulse width  $(t_W)$  for the 25-nm quad-MTJ and the

Fig. 13. Write pulse width ( $t_W$ ) dependence of WER at different write voltage for (a) 25-nm quad-MTJ and (b) 27-nm double-MTJ. The voltage was normalized by double-MTJ with 10 ns. In comparison with the double-MTJ, the quad-MTJ has a sharper WER curve.

Fig. 14. WER down to  $10^{-6}$  for high speed switching at different write voltage (V) for the 34-nm quad-MTJ.

27-nm double-MTJ.  $I_{\rm C}$  of the quad-MTJ shows a larger value than that of the double-MTJ at  $t_{\rm W}$  of 1  $\mu$ s. In contrast,  $I_{\rm C}$  of the quad-MTJ shows a smaller value than that of the double-MTJ in a shorter write pules range ( $t_{\rm W} < 100$  ns), which is a real usage condition. These advantages of 25-nm quad-MTJ are realized by the less sensitiveness against thermal excitation in the case of MTJ with higher  $\Delta$  [10].

# H. Endurance

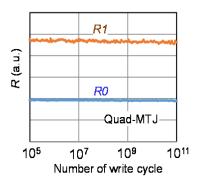

Fig. 17 shows the endurance performance of the 25-nm quad-MTJ; it achieves an endurance of over  $10^{11}$ , while

Fig. 15.  $H_{SW}$  versus  $V_b$  data for (a) quad-MTJ and (b) double-MTJ. Fitting was performed with quadratic functions [26].

Fig. 16. Dependence of the write current ( $I_{\rm C}$ ) on the write pulse width ( $t_{\rm W}$ ) for the 25-nm quad-MTJ and the 27-nm double-MTJ. Although the quad-MTJ has high  $\Delta$ ,  $I_{\rm C}$  of quad-MTJ can be decreased at  $t_{\rm W} < 100$  ns that is real usage condition, compared to that of the double-MTJ.

Fig. 17. Endurance result of the 25-nm quad-MTJ. Although the quad-MTJ enhances  $\Delta$  by a factor of  $\sim 2$ , its endurance exceeds that of a conventional MTJ by at least  $10^{11}$ .

maintaining over ten years retention owing to its higher write efficiency than that of the double-MTJ with low *RA*.

# **IV. CONCLUSION**

We successfully demonstrated a thermally stable quad-MTJ down to 25 nm. As presented in Table I, by developed quad-MTJ technology and low damage fabrication processes, our 25-nm quad-MTJ has a low *RA* of 3  $\Omega\mu m^2$ , twice  $\Delta$  of the double-MTJ, high write efficiency, 10-ns high-speed writing, ten-year retention, and 10<sup>11</sup> endurance at the same time. Moreover, by these developed technologies, advantages of the quad-MTJ such as large  $\Delta$  and high write efficiency are kept even though the quad-MTJ size was scaled down from

#### TABLE I

SUMMARY OF THE DEVELOPED QUAD-MTJ TECHNOLOGY OVER THE DOUBLE-MTJ TECHNOLOGY. THE QUAD-MTJ HAS MORE THAN TEN YEARS OF RETENTION DOWN TO 25 nm,  $10^{11}$  ENDURANCE PERFORMANCE AND LOW *RA* PRODUCT. MOREOVER, ADVANTAGES OF QUAD-MTJ ARE KEPT EVEN THOUGH THE QUAD-MTJ SIZE WAS SCALED DOWN FROM 33 TO 25 nm AND *RA* DECREASED FROM 5 TO 3  $\Omega \mu m^2$

|                                    | Developed 25nm<br>Quad-MTJ<br>in this work | Quad-MTJ<br>at VLSI2020<br>[13]    | Double-MTJ<br>at IEDM2018<br>[4] |

|------------------------------------|--------------------------------------------|------------------------------------|----------------------------------|

| Junction CD                        | 25 nm ~ 🔶                                  | 33 nm ~                            | 55 nm ~                          |

| RA                                 | 3 Ωμm² 🧲                                   | <b>5</b> Ωμm²                      | Not disclosed                    |

| Thermal stability $\Delta$         | Improved by<br>a factor 2 in 25 nm         | Improved by<br>a factor 2 in 3X nm | Factor1 for ∆ in<br>5X nm        |

| Write efficiency $\Delta / I_{c0}$ | Improved by<br>a factor ~1.5@10 ns         | Improved by<br>a factor ~2.2 @10ns | Factor1 for $\Delta$ / $I_{c0}$  |

| Write speed                        | 10 ns @25nm                                | 10 ns @33nm                        | 14 ns                            |

| Retention                          | >10 years @25nm                            | >10 years @33nm                    | >10 years @55nm                  |

| Endurance                          | > 10 <sup>11</sup> @25nm                   | > 10 <sup>11</sup> @33nm           | > 10 <sup>10</sup>               |

33 to 25 nm and *RA* decreased from 5 to 3  $\Omega \mu m^2$ . These quad-MTJ technologies will contribute to the further scaling of the 2× nm STT-MRAM and high reliable STT-MRAM applications, such as automobile and factory automation, etc.

#### REFERENCES

- J. C. Slonczewski, "Current-driven excitation of magnetic multilayers," J. Magn. Magn. Mater., vol. 159, nos. 1–2, pp. L1–L7, Jun. 1996.

- [2] L. Berger, "Emission of spin waves by a magnetic multilayer traversed by a current," *Phys. Rev. B, Condens. Matter*, vol. 54, no. 13, pp. 9353–9358, Oct. 1996.

- [3] E. B. Myers, D. C. Ralph, J. A. Katine, R. N. Louie, and R. A. Buhrman, "Current-induced switching of domains in magnetic multilayer devices," *Science*, vol. 285, no. 5429, pp. 867–870, Aug. 1999.

- [4] S. Ikegawa, F. B. Mancoff, J. Janesky, and S. Aggarwal, "Magnetoresistive random access memory: Present and future," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1407–1419, Apr. 2020.

- [5] Y. K. Lee *et al.*, "Embedded STT-MRAM in 28-nm FDSOI logic process for industrial MCU/IoT application," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2018, pp. 181–182.

- [6] W. J. Gallagher *et al.*, "22 nm STT-MRAM for reflow and automotive uses with high yield, reliability, and magnetic immunity and with performance and shielding options," in *IEDM Tech. Dig.*, Dec. 2019, pp. 2.7.1–2.7.4.

- [7] S. Ikeda *et al.*, "A perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction," *Nature Mater.*, vol. 9, no. 9, pp. 721–724, Jul. 2010.

- [8] H. Sato, M. Yamanouchi, S. Ikeda, S. Fukami, F. Matsukura, and H. Ohno, "Perpendicular-anisotropy CoFeB-MgO magnetic tunnel junctions with a MgO/CoFeB/Ta/CoFeB/MgO recording structure," *Appl. Phys. Lett.*, vol. 101, no. 2, 2012, Art. no. 022414.

- [9] H. Honjo *et al.*, "10 nmφ perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction with over 400°C high thermal tolerance by boron diffusion control," in *Proc. Symp. VLSI Technol.* (VLSI Technol.), Jun. 2015, pp. T160–T161.

- [10] H. Sato *et al.*, "14 ns write speed 128 Mb density embedded STT-MRAM with endurance >10<sup>10</sup> and 10yrs retention@85°C using novel low damage MTJ integration process," in *IEDM Tech. Dig.*, Dec. 2018, p. 608.

- [11] T. Endoh and H. Honjo, "A recent progress of spintronics devices for integrated circuit applications," J. Low Power Electron. Appl., vol. 8, no. 4, p. 44, 2018.

- [12] O. Golonzka et al., "MRAM as embedded non-volatile memory solution for 22FFL FinFET technology," in *IEDM Tech. Dig.*, Dec. 2018, p. 18.1.1.

- [13] Y. J. Song *et al.*, "Demonstration of highly manufacturable STT-MRAM embedded in 28 nm logic," in *IEDM Tech. Dig.*, Dec. 2018, pp. 18.2.1–18.2.2.

- [14] K. Lee et al., "22-nm FD-SOI embedded MRAM technology for lowpower automotive-grade-1 MCU applications," in *IEDM Tech. Dig.*, Dec. 2018, p. 27.1.1.

- [15] J. G. Alzate *et al.*, "2 MB array-level demonstration of STT-MRAM process and performance towards L4 cache applications," in *IEDM Tech. Dig.*, Dec. 2019, p. 2.4.1.

- [16] H. Sato *et al.*, "Properties of magnetic tunnel junctions with a MgO/CoFeB/Ta/CoFeB/MgO recording structure down to junction diameter of 11 nm," *Appl. Phys. Lett.*, vol. 105, no. 6, Aug. 2014, Art. no. 062403.

- [17] K. Nishioka *et al.*, "Novel quad interface MTJ technology and its first demonstration with high thermal stability and switching efficiency for STT-MRAM beyond 2X nm," in *Proc. Symp. VLSI Technol.*, Jun. 2019, pp. T120–T121.

- [18] K. Nishioka *et al.*, "Novel quad-interface MTJ technology and its first demonstration with high thermal stability factor and switching efficiency for STT-MRAM beyond 2X nm," *IEEE Trans. Electron Devices*, vol. 67, no. 3, pp. 995–1000, Mar. 2020.

- [19] S. Miura *et al.*, "Scalability of quad interface p-MTJ for 1X nm STT-MRAM with 10 ns low power write operation, 10 years retention and endurance > 10<sup>11</sup>," *IEEE Trans. Electron Devices*, vol. 67, no. 12, pp. 5368–5373, Dec. 2020.

- [20] B. Jinnai *et al.*, "High-performance shape-anisotropy magnetic tunnel junctions down to 2.3 nm," in *IEDM Tech. Dig.*, Dec. 2020, pp. 24.1–24.6.

- [21] H. Naganuma, H. Sato, S. Ikeda, and T. Endoh, "Micromagnetic simulation of the temperature dependence of the switching energy barrier using string method assuming sidewall damages in perpendicular magnetized magnetic tunnel junctions," *AIP Adv.*, vol. 10, no. 7, Jul. 2020, Art. no. 075106.

- [22] M. Niwa *et al.*, "STEM tomography study on structural features induced by MTJ processing," *Appl. Phys. A, Solids Surf.*, vol. 124, no. 10, p. 724, Oct. 2018.

- [23] D. C. Worledge and P. L. Trouilloud, "Magnetoresistance measurement of unpatterned magnetic tunnel junction wafers by current-in-plane tunneling," *Appl. Phys. Lett.*, vol. 83, no. 1, pp. 84–86, Jul. 2003.

- [24] R. H. Victora and X. Shen, "Composite media for perpendicular magnetic recording," *IEEE Trans. Magn.*, vol. 41, no. 2, pp. 537–542, Feb. 2005.

- [25] R. Bell, J. Hu, and R. H. Victora, "Dual referenced composite free layer design for improved switching efficiency of spin-transfer torque random access memory," *IEEE Electron Device Lett.*, vol. 37, no. 9, pp. 1108–1111, Sep. 2016.

- [26] G. Mihajlović *et al.*, "Origin of the resistance-area-product dependence of spin-transfer-torque switching in perpendicular magnetic randomaccess memory cells," *Phys. Rev. A, Gen. Phys. Appl.*, vol. 13, no. 2, Feb. 2020, Art. no. 024004.