# Online surface code decoder with a superconducting circuit

Special Postdoc Researcher (SPDR)

Superconducting Quantum Computing System Research Unit

RIKEN Center for Quantum Computing

Yosuke Ueno

# Yosuke Ueno (上野洋典)

- Career

- o 2022.3: Ph.D. in Information Sci. and Tech. @ University of Tokyo

- Supervisors: Masaaki Kondo (Keio Univ., R-CCS), Hiroshi Nakamura

- Thesis: Online Quantum Error Correction Using a Superconducting Circuit

- 2022.5 to 2023.2: Guest researcher @ Technical University Munich

- 2023.4 to Present: SPDR @ RIKEN Center for Quantum Computing

- Research interest

- Computer architecture

- Quantum error correction

- Cryogenic computing

My first and last beer in Germany

# Summary of this talk

- Decoding surface code is reduced to graph matching problem

- A practical decoder should be <u>accurate</u>, <u>fast</u>, <u>and scalable</u>

- For superconducting QCs, decoder also should be power efficient to be operated in a cryogenic environment

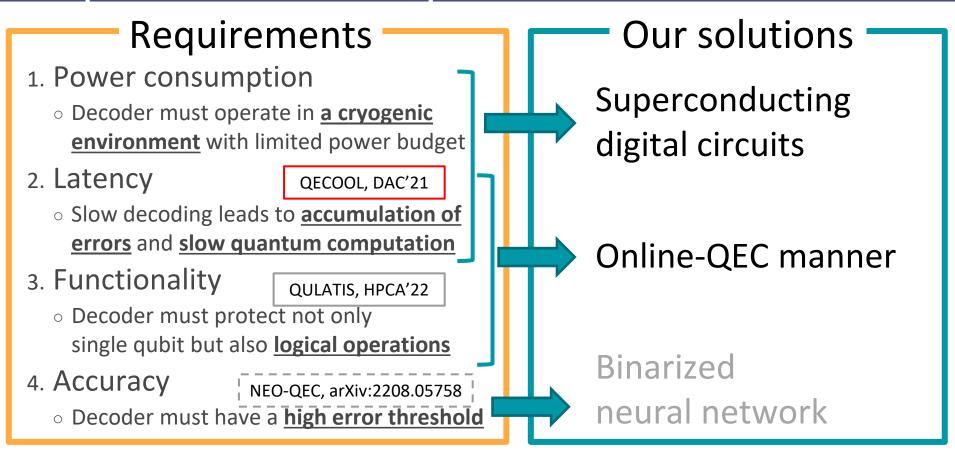

- Our solution: online decoder with superconducting digital circuit

- QECOOL: Online decoder with superconducting circuits (DAC'21, arXiv:2103.14209)

- QULAIS: Extension of QECOOL for logical operation with lattice surgery (HPCA'22)

- NEO-QEC: Extension of QECOOL/QULATIS with binarized NN for better accuracy (arXiv:2208.05758)

### Outline

- Introduction

- Superconducting quantum computer

- Quantum error correction with surface code

- Requirements for a practical decoder

- QECOOL: online decoder with a superconducting circuit

- QULATIS: online superconducting decoder for lattice surgery

- Summary

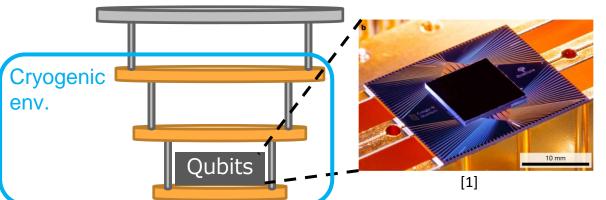

# Superconducting quantum computer (QC)

Dilution refrigerator

- # of qubits: around 100

- Error rate: 1%

- Noisy Intermediate Scale

Quantum (NISQ) device

- Superconducting qubit: one of the most promising qubit implementation

- Operate only at cryogenic environment (~20 mK)

- Qubits have very low error tolerance

- Quantum error correction (QEC) code

[1] Frank Arute, Kunal Arya, Ryan Babbush, et al., Quantum supremacy using a programmable superconducting processor, Nature 574, 505–510 (2019).

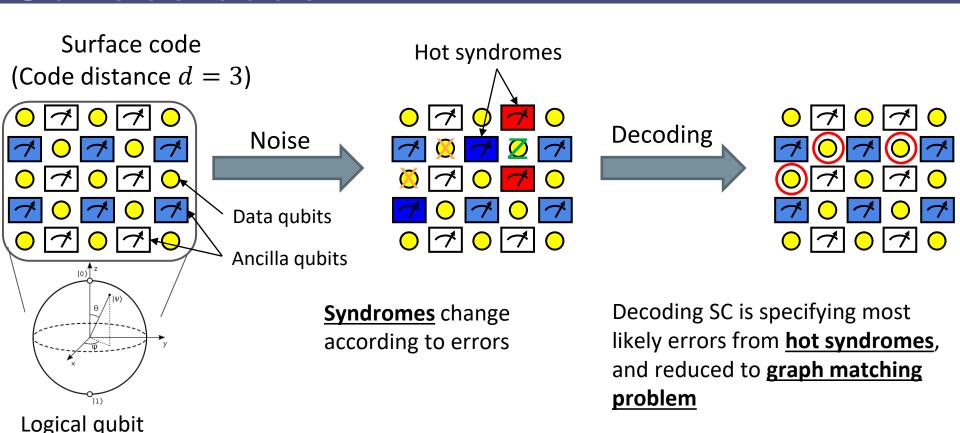

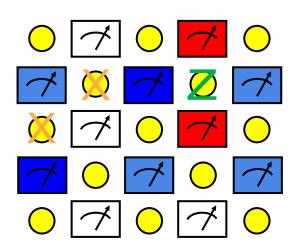

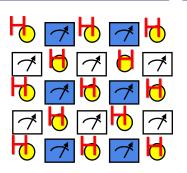

### Surface code

## Function of surface code

- Each ancilla qubit is used for error parity detection of neighboring data qubits

- Endpoints of error chains are expected to be <u>hot syndromes</u>

- Errors on data qubit can be detected without direct measurement

### Decoding surface code

#### Assumption

- X and Z errors can be decoded independently

- Shorter error chains are likely to occur

Minimum Weight Perfect Matching (MWPM)

*V*: Hot syndromes

$W_e$ : Manhattan distance

Exact solution: Blossom algorithm (O(n3))

### Decoding surface code

#### Assumption

- X and Z errors can be decoded independently

- Shorter error chains are likely to occur

Minimum Weight Perfect Matching (MWPM)

*V*: Hot syndromes

$W_e$ : Manhattan distance

Exact solution: Blossom algorithm (O(n3))

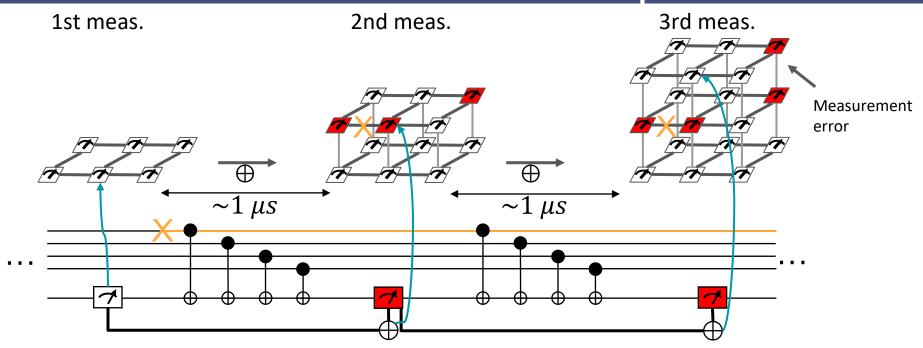

### Measurement error on ancilla qubit

- If ancilla qubit measurement is susceptible to read errors, multiple measurement processes are required

- o For every new measurement, the new syndrome is **XORed** with the latest value

### Outline

- Introduction

- Superconducting quantum computer

- Quantum error correction with surface code

- Requirements for a practical decoder

- QECOOL: online decoder with a superconducting circuit

- QULATIS: online superconducting decoder for lattice surgery

- Summary

## Requirements for a practical decoder

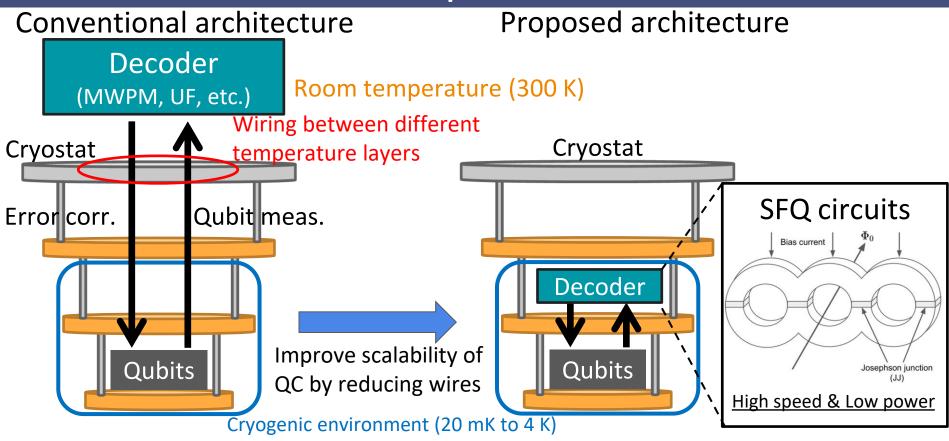

### QEC architecture for supercond. QCs

Power budget ~ 1 W

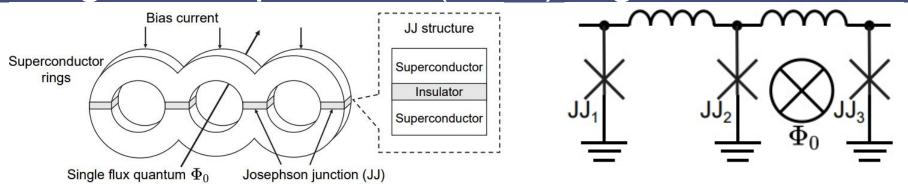

### Single flux quantum (SFQ) logic

- Absence (presence) of flux quanta within the ring represents digital '0' ('1')

- Operates only in a cryogenic environment (~ 4 K)

- High speed and low latency compared to CMOS circuits

- Limitation: Large amount of RAM is expensive

- -> Conventional decoders such as MWPM are not implementable with SFQ

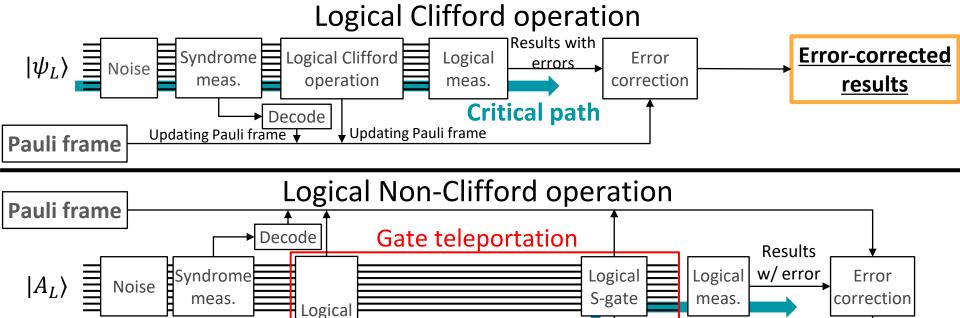

**Critical path**

Error-

<del>corrected</del>

result

### Impact of decoding latency

**CNOT**

Decode

Logical

meas.

Syndrome

meas.

Noise

Pauli frame

**Error**

correction

**Error-corrected**

results

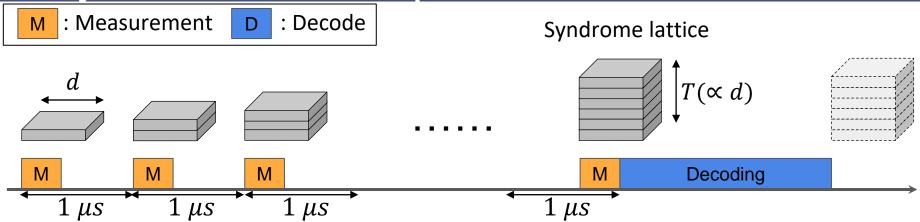

### Why is MWPM not practical?

Measurement and decoding processes with the MWPM decoder

#### Batch-QEC manner

- + Accurate decoding

- Slow decoding

- $-O(Td^2)$  bits of storage

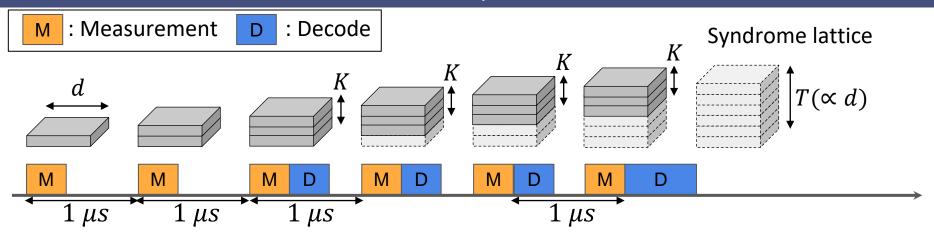

### Our solution: Online-QEC manner

Measurement and decoding processes with a practical decoder

#### Online-QEC manner

- Degradation of decoding accuracy

- + Fast decoding

- +  $O(Kd^2)$  bits of storage

### Outline

- Introduction

- Superconducting quantum computer

- Quantum error correction with surface code

- Requirements for a practical decoder

- QECOOL: online decoder with a superconducting circuit

- QULATIS: online superconducting decoder for lattice surgery

- Summary

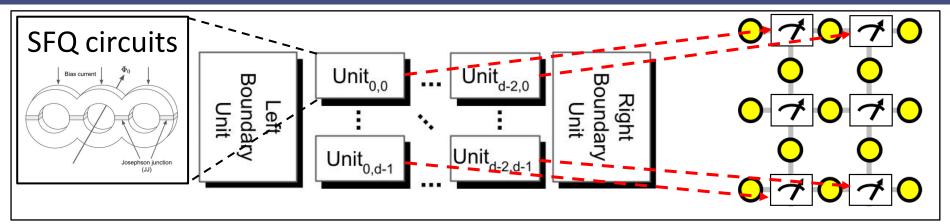

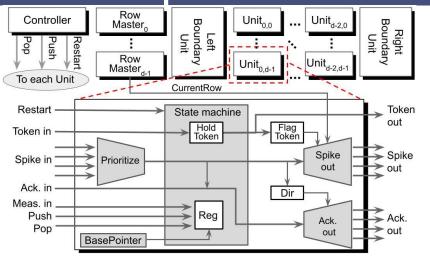

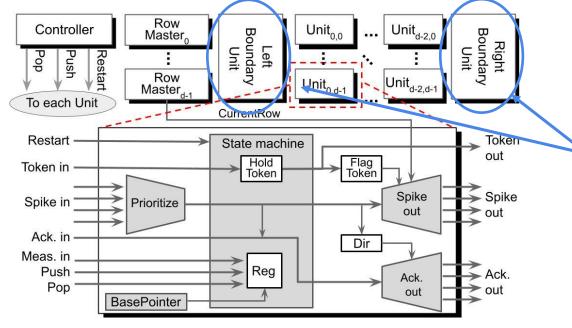

### **QECOOL**

Architecture overview of QECOOL decoder

- Quantum Error COrrection by On-Line decoding algorithm

- A distributed architecture without large amount of RAM

- Multiple processing elements (<u>Units</u>) corresponding one-to-one with ancilla qubits

- Matching problems are solved by signal propagation among Units

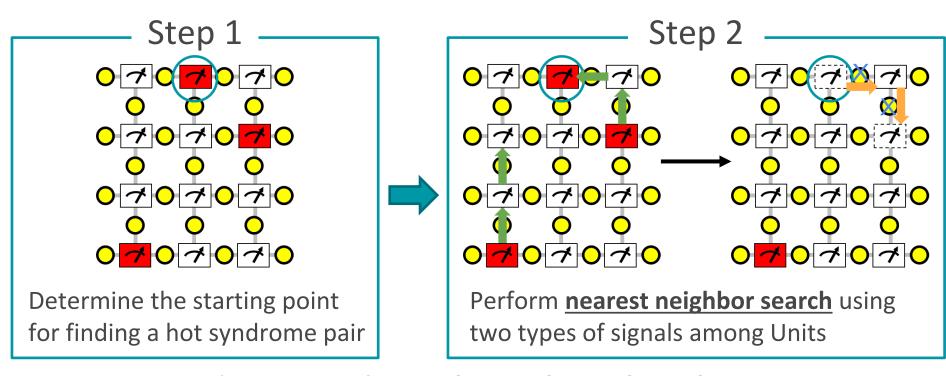

# Overview of QECOOL algorithm

Based on a greedy graph matching algorithm

$O(n^2)$ , approximation degree 1/2

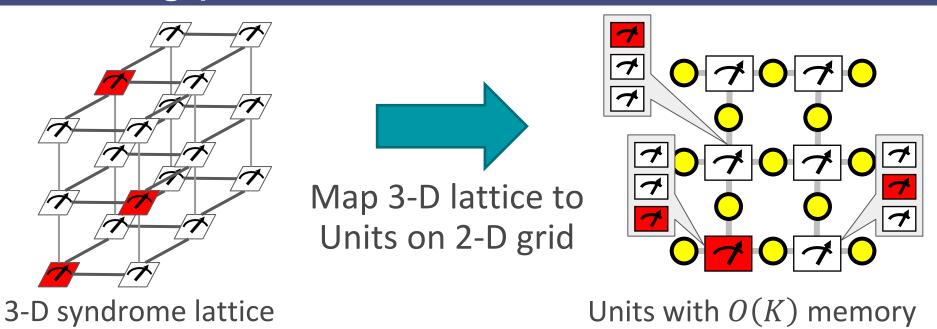

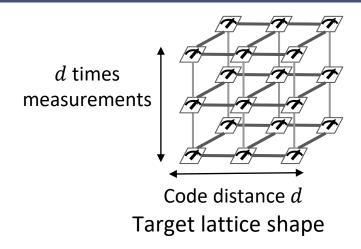

# Matching problem on a 3-D lattice

- Each Unit has a O(K) buffer to store multiple syndrome values

- Almost the same procedure as in case of 2-D lattice

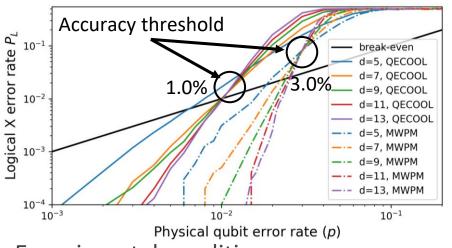

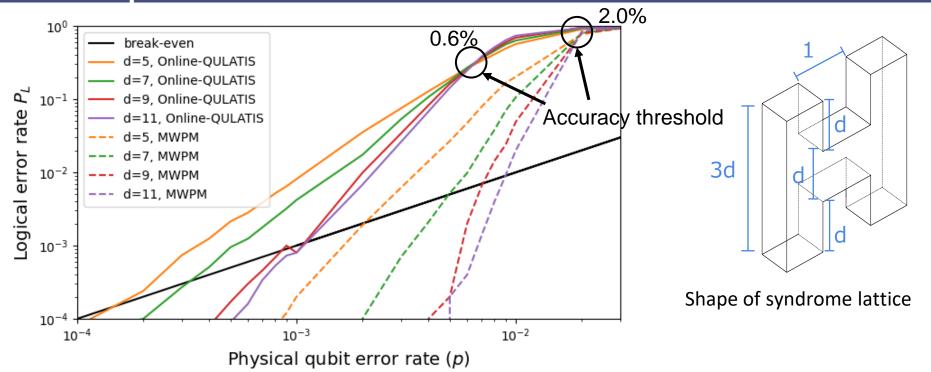

# Decoding performance of QECOOL

#### **Experimental condition**

- Measurement process is performed once every 1  $\mu s$

- Each QECOOL Unit has a **7-bit** buffer to store syndrome values

- If buffer entry size is greater than K=3, QECOOL is performed; otherwise, each Unit waits for measurement process

- MWPM operates with batch-QEC manner

- Threshold value: QECOOL p=0.01, MWPM p=0.03

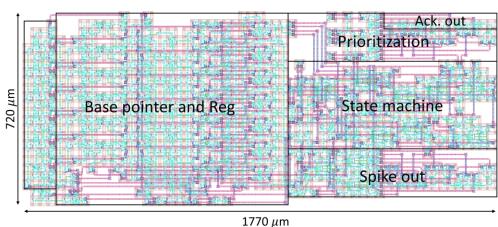

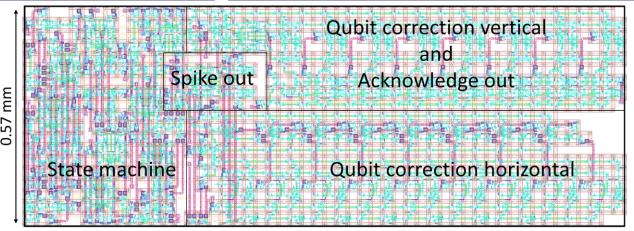

### SFQ implementation of QECOOL decoder

Architecture overview of QECOOL

SFQ design layout of QECOOL Unit

JJs: 3177

Area: 1.274 mm<sup>2</sup>

Latency: 215 ps

Power cons.: **2.78 μW**

#### # of protectable logical qubits on 4-K environment

Suppose d=9, and power budget in 4-K env. is 1 W

$$1_{[W]}/(9 \times 8 \times 2 \times 2.78_{[\mu W]}) = 2498$$

logical qubits

# Summary of QECOOL

- Online decoding of surface code in a cryogenic environment is necessary for a scalable superconducting quantum computer

- QECOOL decoder with SFQ implementation is power-efficient and fast to operate in a 4-K environment within code cycle (1  $\mu$ s)

- QECOOL is capable of decoding a <u>single logical qubit</u> with measurement errors

Requirements for practical decoder

- ✓ Power consumption

- √ Latency

Functionality

Accuracy

### Outline

- Introduction

- Superconducting quantum computer

- Quantum error correction with surface code

- Requirements for a practical decoder

- QECOOL: online decoder with a superconducting circuit

- QULATIS: online superconducting decoder for lattice surgery

- Summary

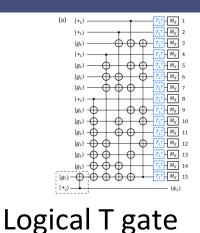

#### Req 3. Functionality

# Protecting logical {*H*, CNOT, *T*}

Logical Hadamard

Performed

straightforwardly

Logical CNOT

Performed by

Lattice surgery

Performed by **logical** *H* **and CNOT operations**

(+ magic state & gate teleportation)

<u>Decoding lattice surgery</u> is essential for fault-tolerant universal quantum computation

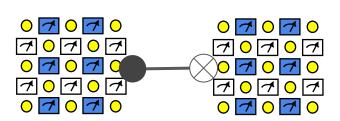

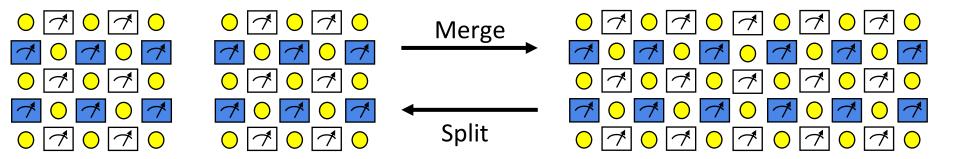

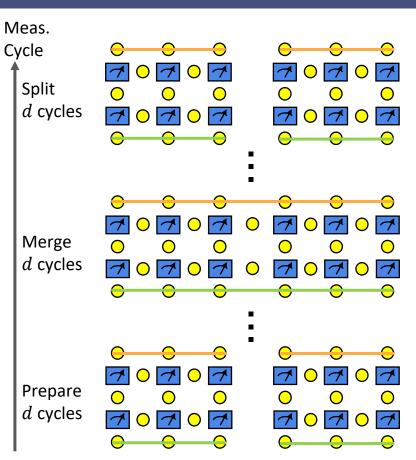

# Lattice surgery (LS)

- Framework to perform logical operations with SC-based QEC

- Implement logical Pauli measurements on multiple logical qubits by merging and splitting two of them

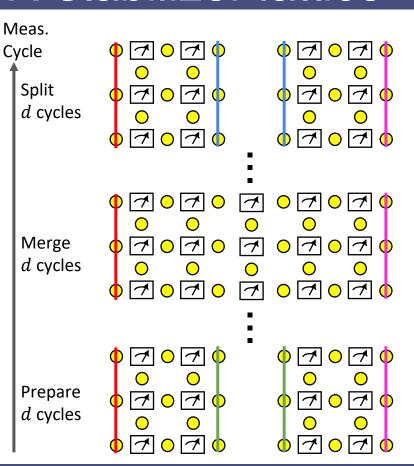

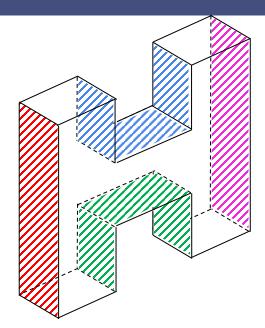

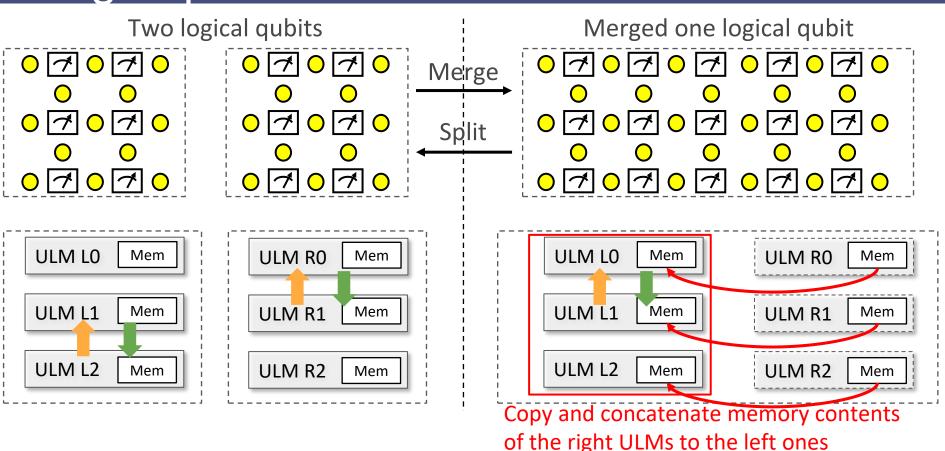

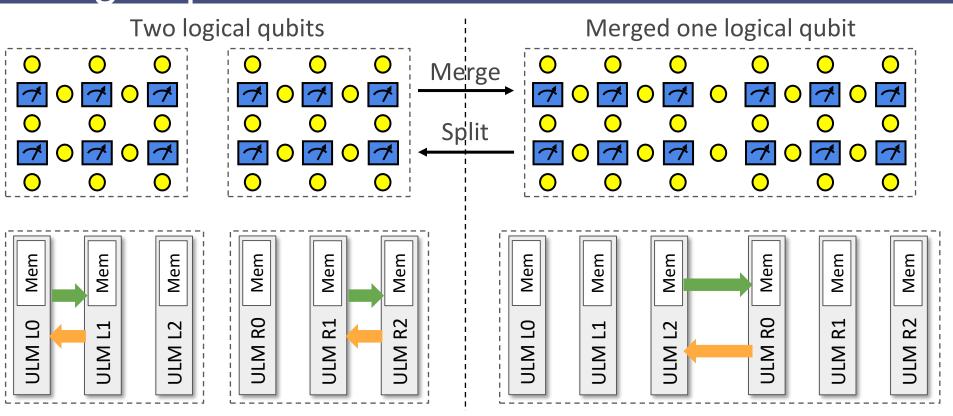

### Merge and split operation

- <u>Pauli-XX</u> and <u>Pauli-ZZ</u> measurements are realized by merge and split operation

- Logical CNOT operation is realized by Pauli-XX and Pauli-ZZ measurements

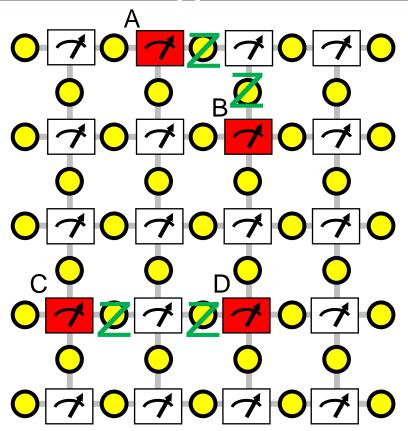

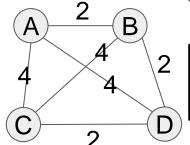

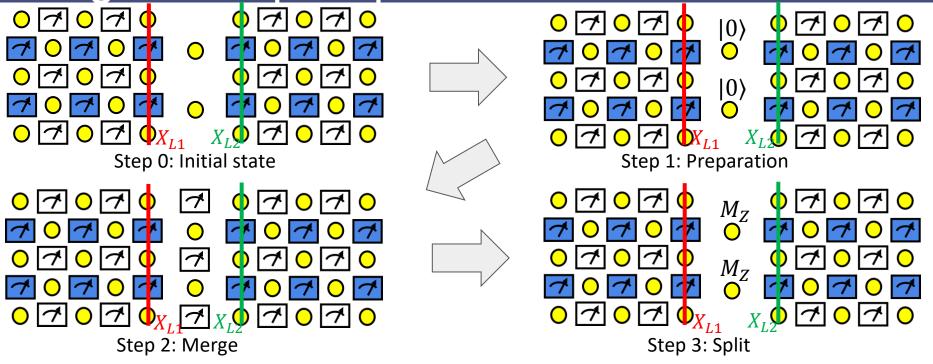

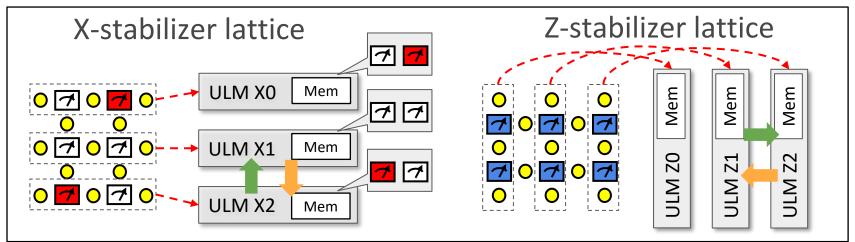

### Decoding process of LS

### X-stabilizer lattice

#### Boundaries of X-stabilizer lattice

**Left** - Right:  $Z_0Z_1$  error

Left - Upper or Lower saddle:  $Z_0I_1$  error

Right - Upper or Lower saddle:  $I_0Z_1$  error

Upper - Lower saddle: Measurement error

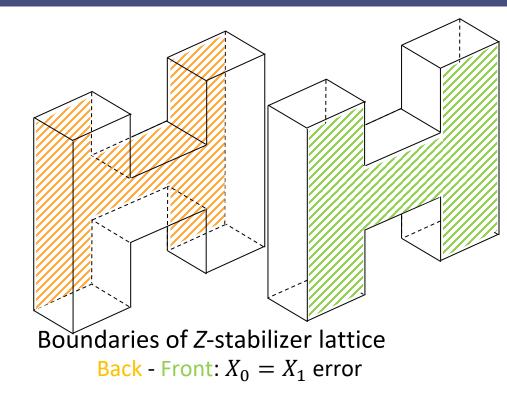

### Z-stabilizer lattice

### Limitation of QECOOL

Boundary Unit

Hardware modules for

boundary matching

Architecture of QECOOL

The hardware modules cannot handle dynamic boundary changes required for LS procedures

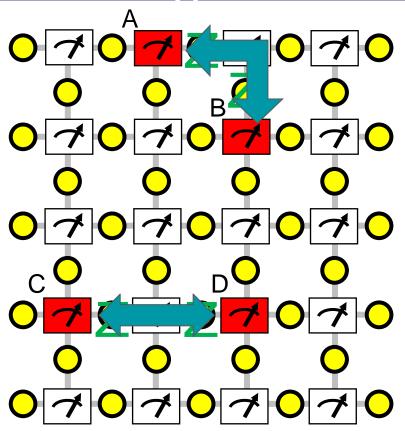

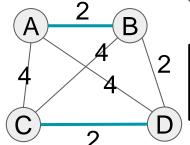

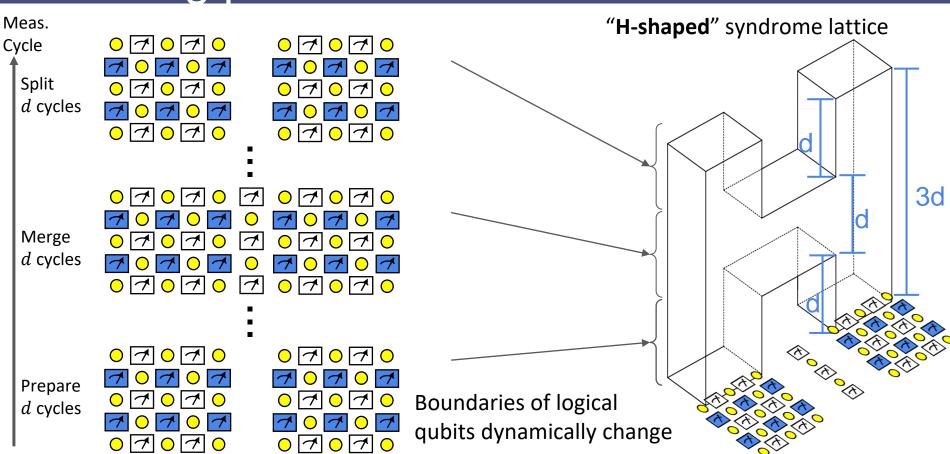

### Overview of QULATIS

- QUantum error correction methodology toward <u>LATtlce Surgery</u>

- Introduce decoding unit named <u>united line module (ULM)</u>

- Associated with horizontal or vertical line of ancilla qubits

- Token, Spike and Acknowledge signals between adjacent ULMs to pair hot syndromes

Architecture overview of QECOOL decoder

### Merge operation of X-stabilizer lattice

### Merge operation of Z-stabilizer lattice

### QEC performance of QULATIS

Error model: depolarizing noise model ([I, X, Z, Y] = [1 - p, p/3, p/3, p/3])

MWPM: batch-QEC

QULATIS: online-QEC (buffer size = 7, operating frequency = 2 GHz)

### SFQ design of ULM

SFQ design of ULM except memory module

Total: 2412 JJs

Area: 0.889 mm<sup>2</sup>

Latency: 157.5 ps

Power : **2.07 μW** @2 GHz

1.56 mm

- Memory module is assumed to be a 64-kb hybrid

SFQ-CMOS memory array proposed by Van Duzer et al.[4]

- Readout delay 400 ns, power 12 mW@1 GHz, 4 K

- 2395 distance-9 logical qubits can be protected in a cryogenic environment in terms of power consumption

[4] Theodore Van Duzer, Lizhen Zheng, Stephen Whiteley, Hoki Kim, Jaewoo Kim, Xiaofan Meng, and Thomas Ortlepp. 64-kb hybrid Josephson-CMOS 4 Kelvin RAM With 400 ps access time and 12 mW read power. IEEE Transactions on Applied Superconductivity, vol. 23, no. 3

# Summary of QULATIS

- Lattice surgery and its decoding are essential for fault-tolerant universal quantum computation

- We propose QULATIS to decode lattice surgery

- Accuracy threshold value: 0.6% for merge-and-split operation

- We design superconducting decoder based on QULATIS

- o 2395 logical qubit can be protected in a cryogenic environment

#### Requirements for practical decoder

- ✓ Power consumption

- √ Latency

- √ Functionality

- Accuracy

### Outline

- Introduction

- Superconducting quantum computer

- Quantum error correction with surface code

- Requirements for a practical decoder

- QECOOL: online decoder with a superconducting circuit

- QULATIS: online superconducting decoder for lattice surgery

- Summary

# Summary

- Online decoding of surface code in a cryogenic environment is necessary for a scalable superconducting quantum computer

- **QECOOL** decoder is power-efficient enough to protect around 2500 logical qubits with distance-9 SC in a cryogenic env.

- QULATIS is an extension of QECOOL, which supports logical operations via lattice surgery

- Accuracy of QECOOL and QULATIS is lower than MWPM due to its greedy and online nature

- <u>NEO-QEC</u>: Extension of QECOOL/QULATIS with binarized NN for better accuracy (arXiv:2208.05758)