# Inter-temperature Bandwidth Reduction in Cryogenic QAOA machines

超伝導量子計算機のシステムレベル最適化に向けて~QAOAを対象とした場合~

Yosuke Ueno<sup>1, 2, 3</sup>, Yuna Tomida<sup>2</sup>, Teruo Tanimoto<sup>3</sup>, Masamitsu Tanaka<sup>4</sup>, Yutaka Tabuchi<sup>1</sup>, Koji Inoue<sup>3</sup>, Hiroshi Nakamura<sup>2</sup> 2 The University of Tokyo 3 Kyushu University 4 Nagoya University

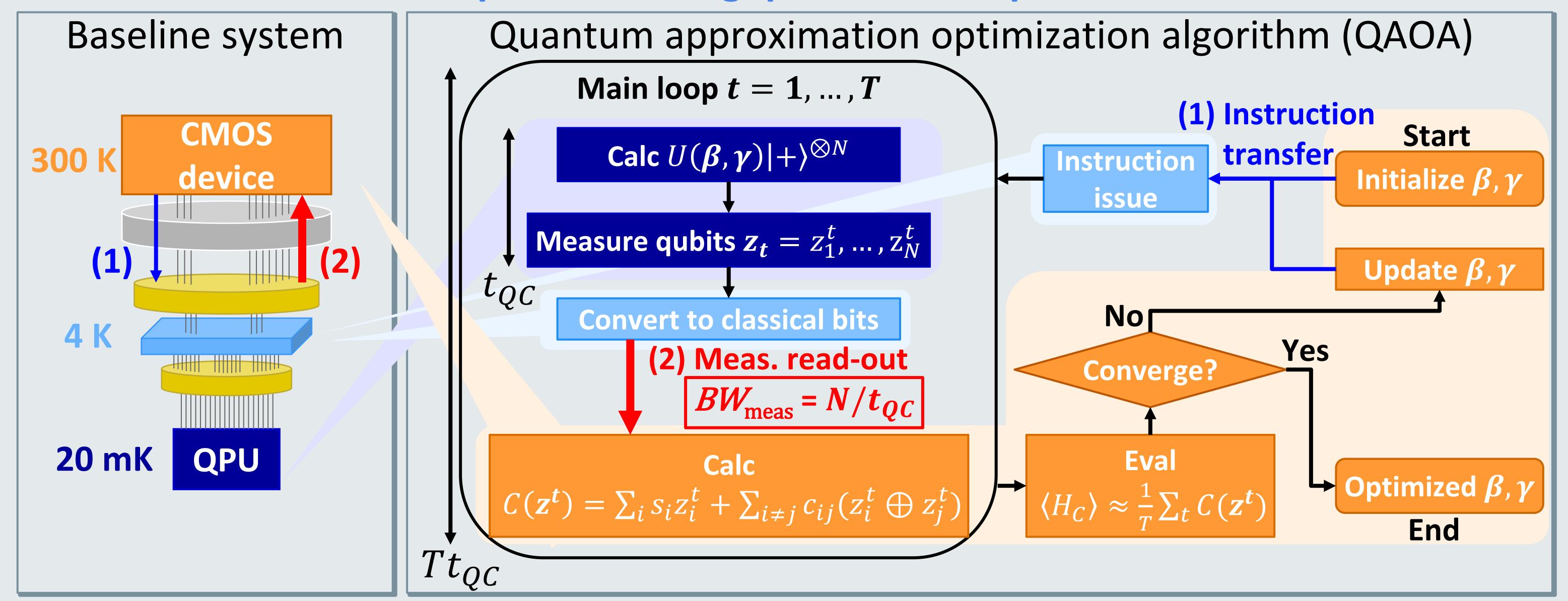

## # QAOA execution on a superconducting quantum computer

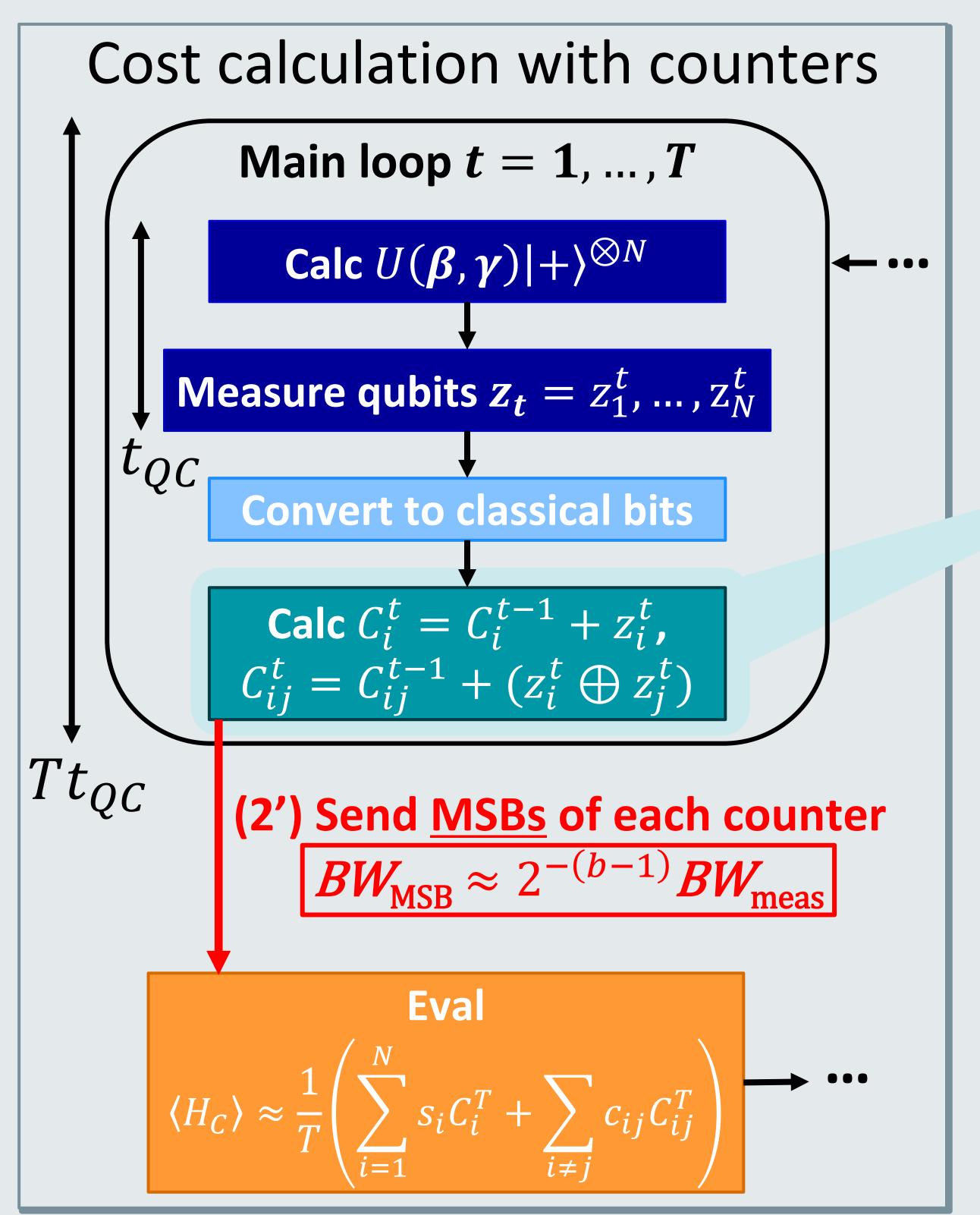

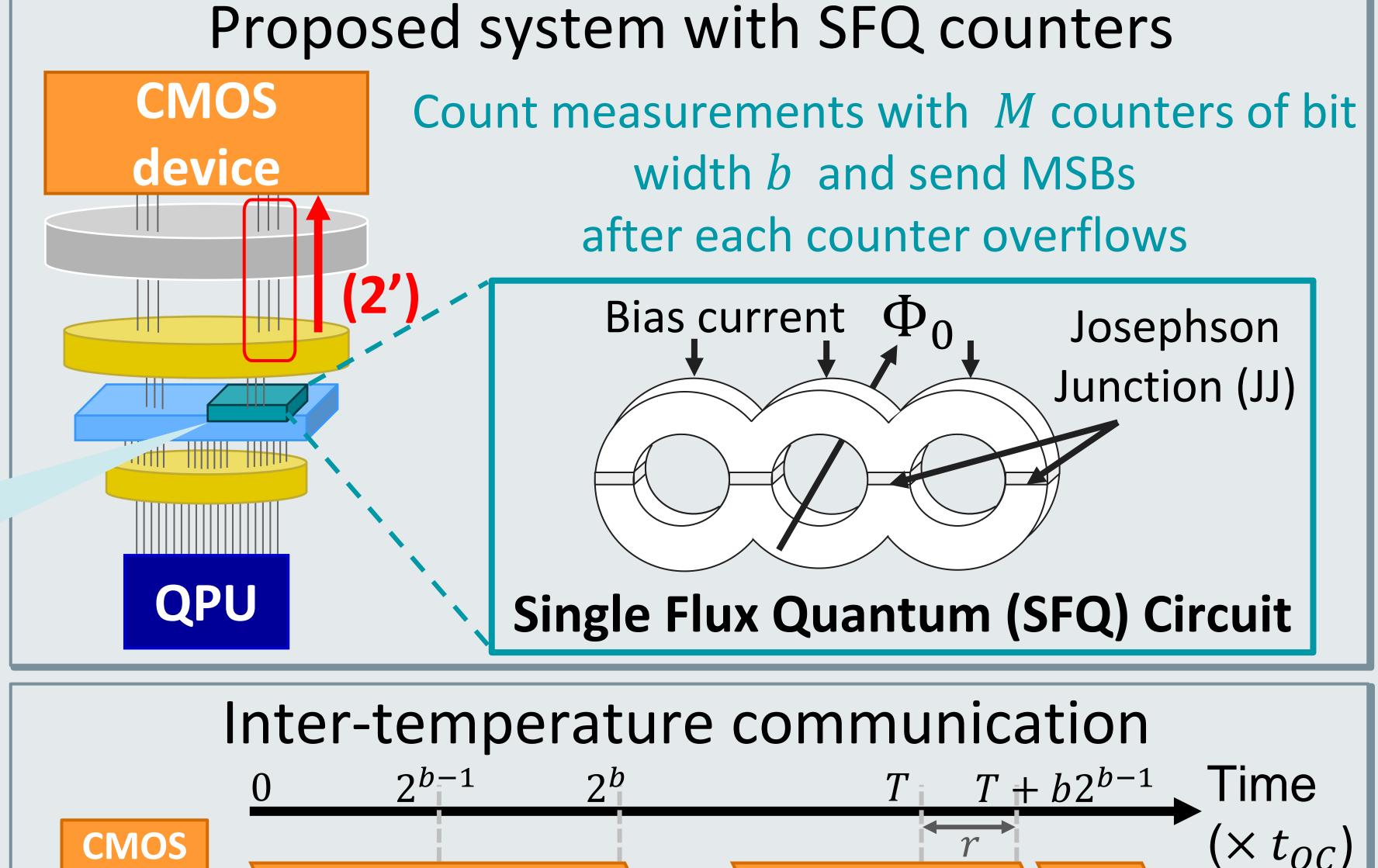

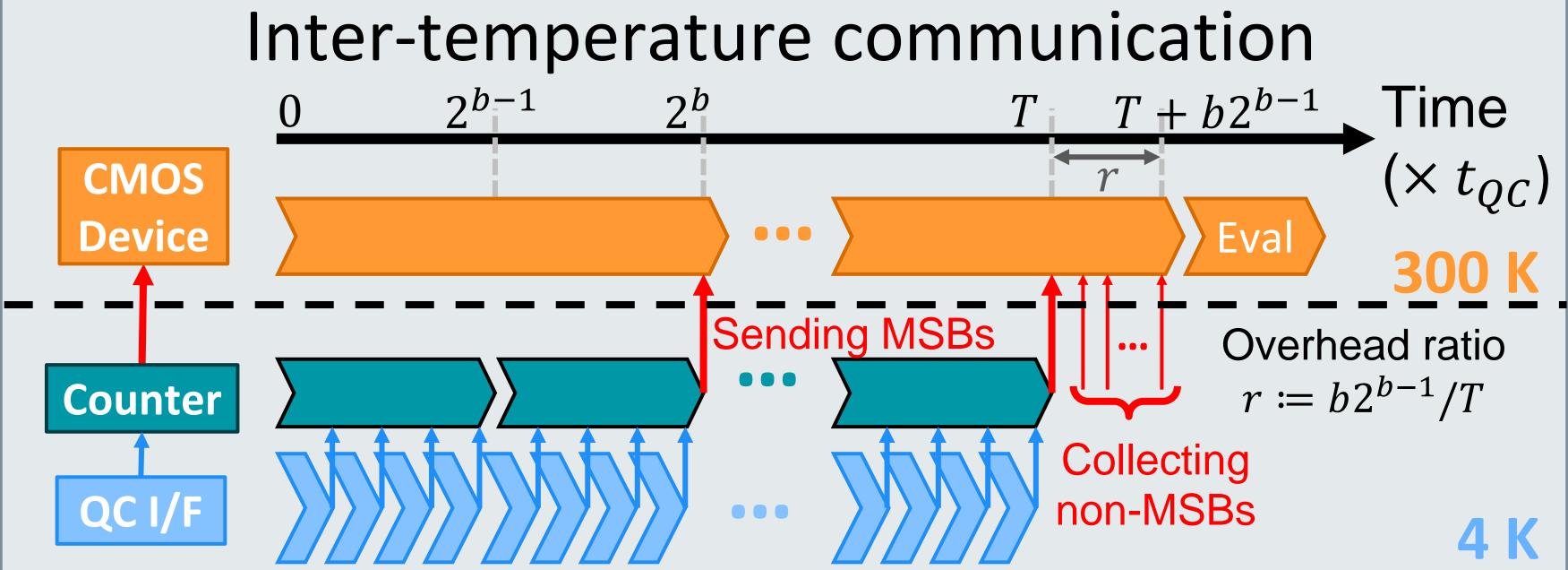

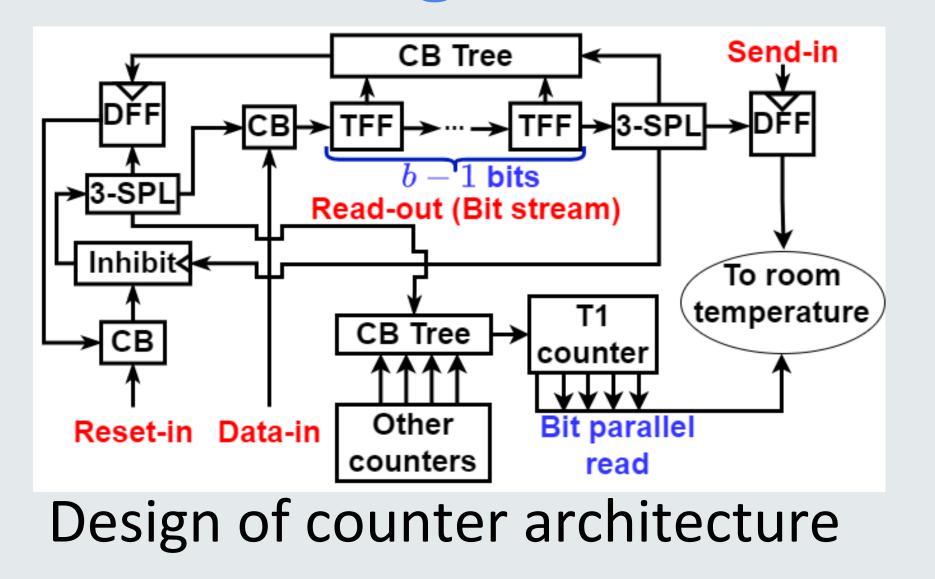

### # Counter-based architecture for measurement bandwidth reduction

# # Circuit design

JJs: 11b+31 Power: 9.71b+16.8 (pW)

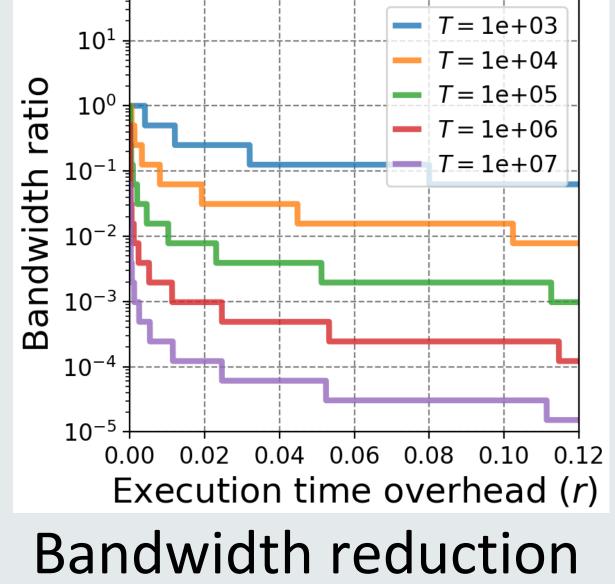

#### # Evaluation

to time overhead r

#### **©** Configuration Required bandwidth Power dissipation · 20 <del>(</del>5) Baseline Baseline Cable: Proposed, b = 3Proposed. b = 3dissipation 100 Proposed, $b = \lceil \log_2 N \rceil$ 2000 Power 50 4000 5000 6000 7000 Number of qubits (N)

Power dissipations (heat inflow and power consumption)

#### Bandwidth: 1 Gbps SFQ counter:

Power: 9.71b+16.8 (pW) : N(N+1)/2

Heat inflow: 1.0 mW

Peripheral: 10.5 mW

# # Summary

Our method reduced the communication during QAOA by transferring the MSB of SFQ counters. Our architecture achieved exponential bandwidth reduction and decreased cables power dissipation in a cryogenic environment with the negligible power overhead.